| Pro       | oduct List                                                   | 3  |

|-----------|--------------------------------------------------------------|----|

| Des       | escription                                                   | 3  |

| Ord       | dering Information                                           | 3  |

|           | atures                                                       |    |

|           | n Configuration                                              |    |

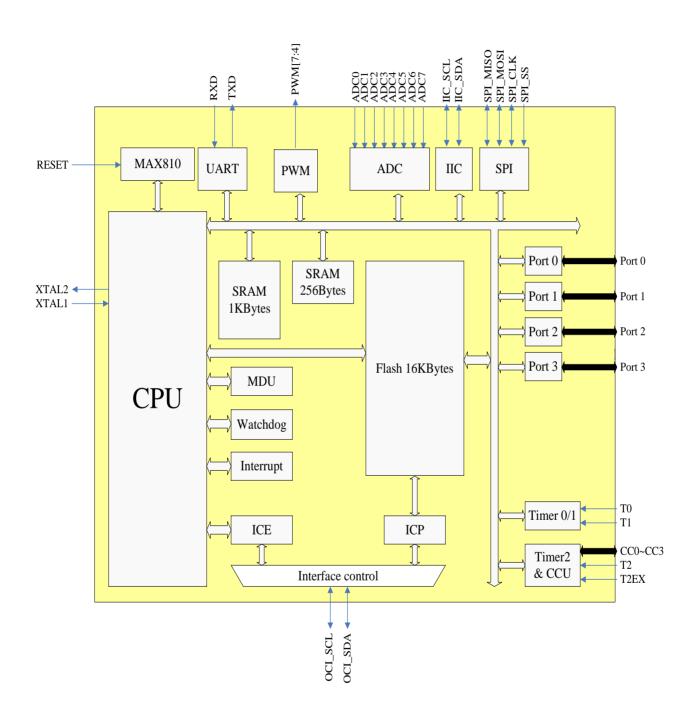

|           | ock Diagram                                                  |    |

|           | ecial Function Register (SFR)                                |    |

|           | nction Description                                           |    |

| гиі<br>1. |                                                              |    |

| ١.        | General Features                                             |    |

|           | 1.1 Embedded Flash                                           |    |

|           | 1.2 IO Pads                                                  |    |

|           | 1.3 Instruction timing Selection                             |    |

|           | 1.4 Clock Out Selection                                      |    |

|           | 1.5 RESET                                                    |    |

|           | 1.5.1 Hardware RESET function                                | 15 |

|           | 1.5.2 Software RESET function                                | 15 |

|           | 1.5.3 Reset status                                           | 16 |

|           | 1.5.4 Time Access Key register (TAKEY)                       |    |

|           | 1.5.5 Software Reset register (SWRES)                        |    |

|           | 1.5.6 Example of software reset                              |    |

|           | 1.6 Clocks                                                   |    |

| 2.        | Instruction Set                                              |    |

| ۷.<br>3.  |                                                              |    |

| ა.        | Memory Structure                                             |    |

|           | 3.1 Program Memory                                           |    |

|           | 3.2 Data Memory                                              |    |

|           | 3.3 Data memory - lower 128 byte (00h to 7Fh)                |    |

|           | 3.4 Data memory - higher 128 byte (80h to FFh)               |    |

|           | 3.5 Data memory - Expanded 1K Bytes ( 0000h ~ 03FFh)         |    |

| 4.        | CPU Engine                                                   |    |

|           | 4.1 Accumulator                                              | 24 |

|           | 4.2 B Register                                               | 24 |

|           | 4.3 Program Status Word                                      | 25 |

|           | 4.4 Stack Pointer                                            |    |

|           | 4.5 Data Pointer                                             |    |

|           | 4.6 Data Pointer 1                                           |    |

|           | 4.7 Clock control register                                   |    |

|           | 4.8 Interface control register                               |    |

|           | 4.9 PAGESEL (Page Select)                                    |    |

| 5.        | GPIO                                                         |    |

| J.        |                                                              |    |

|           |                                                              |    |

| _         | 5.2 Software of Writer Setting Method                        |    |

| 6.        | Multiplication Division unit                                 |    |

|           | 6.1 Operating registers of the MDU                           |    |

|           | 6.2 Operation of the MDU                                     |    |

|           | 6.2.1 First phase: Loading the MDx registers                 |    |

|           | 6.2.2 Second phase: Executing calculation                    | 32 |

|           | 6.2.3 Third phase: Reading the result from the MDx registers | 33 |

|           | 6.3 Normalizing                                              | 33 |

|           | 6.4 Shifting                                                 |    |

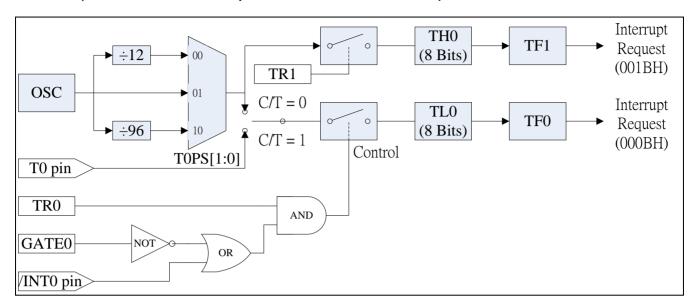

| 7.        | Timer 0 and Timer 1                                          |    |

| • •       | 7.1 Timer/Counter mode control register (TMOD)               |    |

|           | 7.2 Timer/counter control register (TCON)                    |    |

|           | 7.3 Enhance Interrupt Trigger SFR(ENHIT)                     |    |

|           |                                                              |    |

|           | 7.4 Peripheral Frequency control register                    |    |

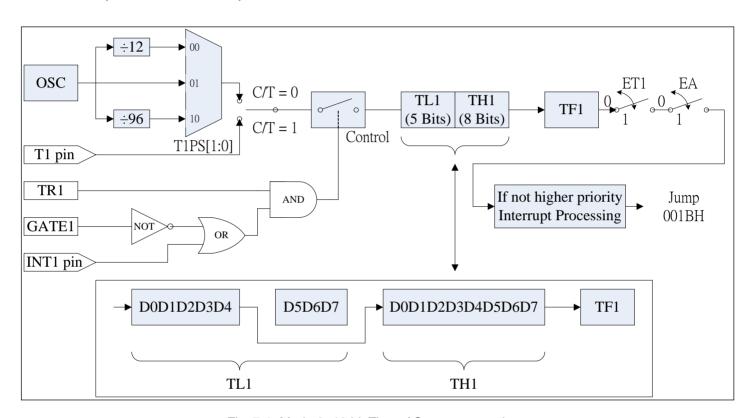

|           | 7.5 Mode 0 (13-bit Counter/Timer)                            |    |

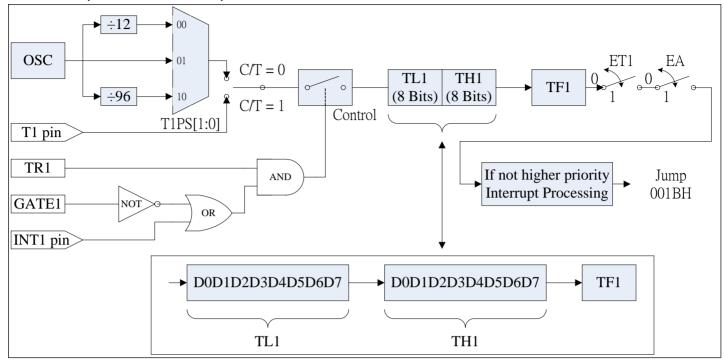

|           | 7.6 Mode 1 (16-bit Counter/Timer)                            | 38 |

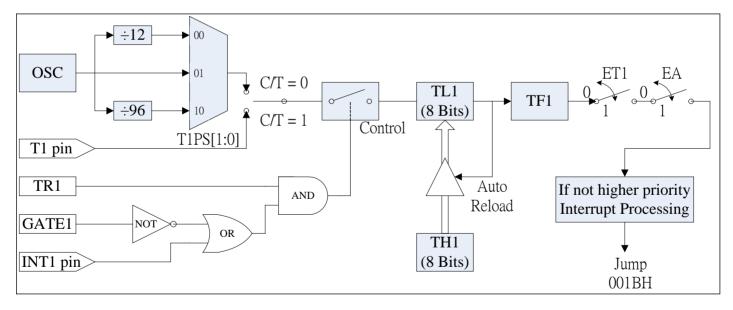

|     | 7.7 Mode       | 2 (8-bit auto-reload Counter/Timer)                         | 38 |

|-----|----------------|-------------------------------------------------------------|----|

|     |                | 3 (Timer 0 acts as two independent 8 bit Timers / Counters) |    |

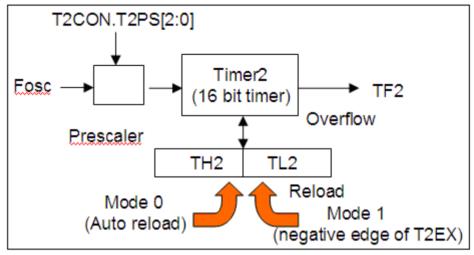

| 8.  |                | d Capture Compare Unit                                      |    |

|     |                | 2 function                                                  |    |

|     |                | Timer mode                                                  |    |

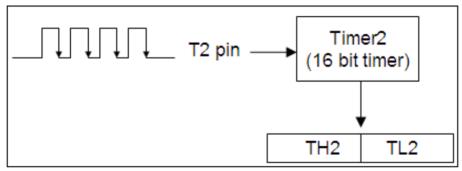

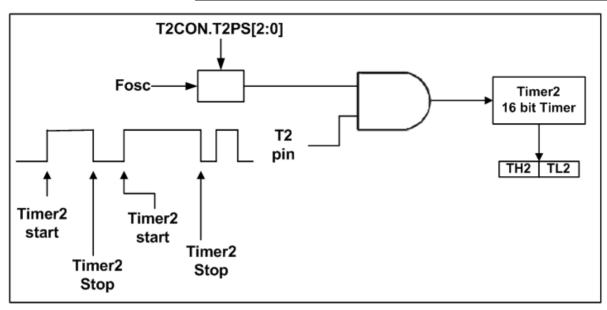

|     | 8.1.2          | Event counter mode                                          | 43 |

|     |                | Gated timer mode                                            |    |

|     |                | Reload of Timer 2                                           |    |

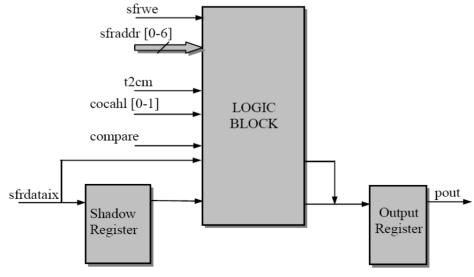

|     |                | are function                                                |    |

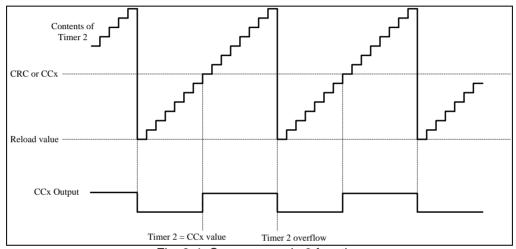

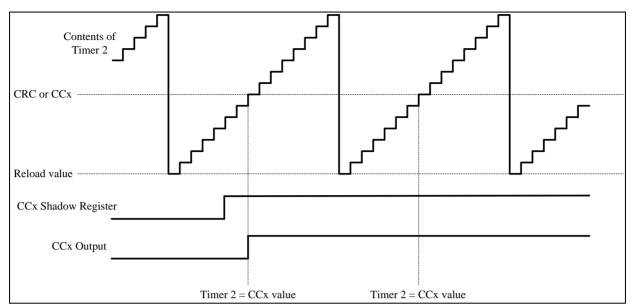

|     |                | Compare Mode 0                                              |    |

|     |                | Compare Mode 1                                              |    |

|     |                | re function                                                 |    |

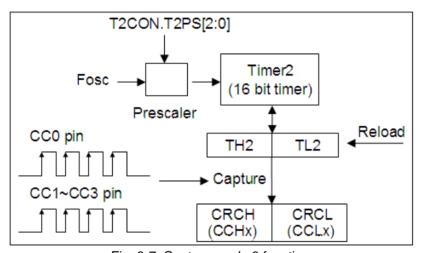

|     |                | Capture Mode 0 (by Hardware)                                |    |

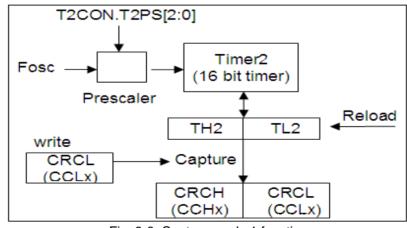

|     |                | Capture Mode 1(by Software)                                 |    |

| 9.  |                | ace                                                         |    |

|     |                | interface                                                   |    |

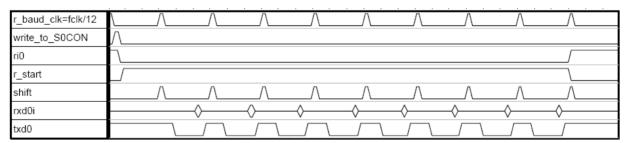

|     |                | Mode 0                                                      |    |

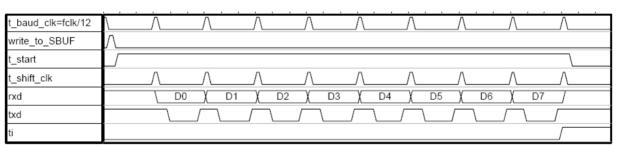

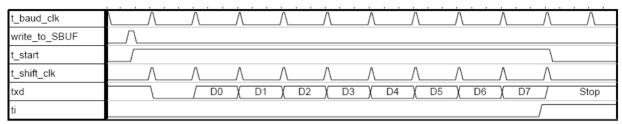

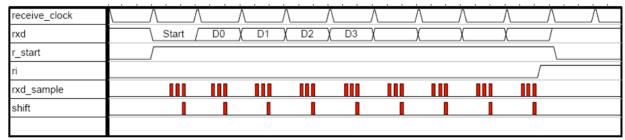

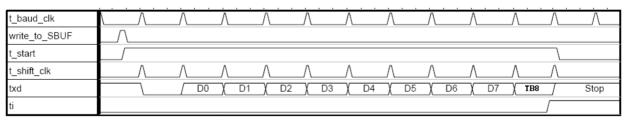

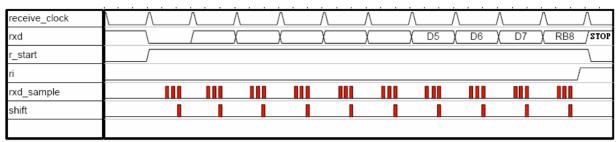

|     |                | Mode 1                                                      |    |

|     |                | Mode 2                                                      |    |

|     |                | Mode 3                                                      |    |

|     |                | rocessor Communication of Serial Interface                  |    |

|     |                | neral Frequency control register                            |    |

|     |                | rate generator                                              |    |

|     |                | Serial interface modes 1 and 3                              |    |

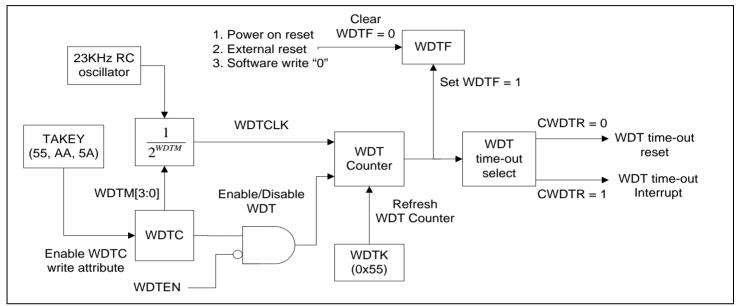

| 10. |                | imer                                                        |    |

| 11. |                |                                                             |    |

|     |                | y level structure                                           |    |

| 12. |                | agement Unit                                                |    |

|     |                | ode                                                         |    |

|     |                | node                                                        |    |

| 13. |                | n Modulation (PWM)                                          |    |

| 14. |                |                                                             |    |

| 15. |                | on - Serial Peripheral Interface                            |    |

| 16. |                | - Low Voltage Interrupt and Low Voltage Reset               |    |

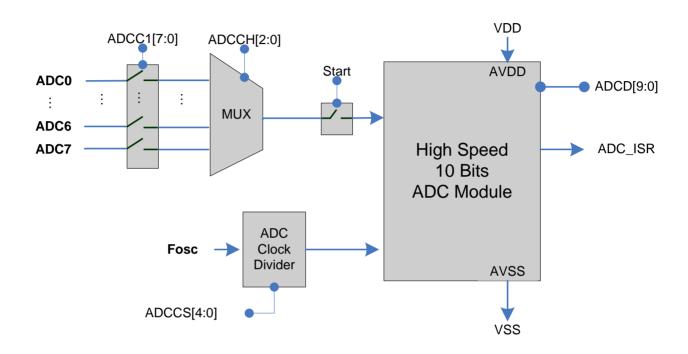

| 17. |                | og-to-Digital Converter (ADC)                               |    |

| 18. |                | Programming (Internal ISP)                                  |    |

|     |                | ervice program                                              |    |

|     |                | Bit (N)                                                     |    |

|     |                | am the ISP Service Program                                  |    |

|     | -              | e ISP Service Program                                       |    |

|     |                | egister – TAKEY, IFCON, ISPFAH, ISPFAL, ISPFD and ISPFC     |    |

| Ope |                | 15                                                          |    |

|     |                |                                                             |    |

|     | & LVR Characte |                                                             |    |

# **Product List**

SM39R16A6U24, SM39R16A6U28, SM39R16A6U32,

# **Description**

The SM39R16A6 is a 1T (one machine cycle per clock) single-chip 8-bit microcontroller. It has 16K-byte embedded Flash for program, and executes all ASM51 instructions fully compatible with MCS-51

SM39R16A6 contains 1K+256B on-chip RAM, up to 30 GPIOs (32L package), various serial interfaces and many peripheral functions as described below. It can be programmed via writers. Its on-chip ICE is convenient for users in verification during development stage.

The high performance of SM39R16A6 can achieve complicated manipulation within short time. About one third of the instructions are pure 1T, and the average speed is 8 times of traditional 8051, the fastest one among all the 1T 51-series.Its excellent EMI and ESD characteristics are advantageous for many different applications.

# **Ordering Information**

SM39R16A6ihhkL

YWW

i: process identifier { U = 1.8V ~ 5.5V}

hh: pin count

k: package type postfix {as table below }

L:PB Free identifier

{No text is Non-PB free, "P" is PB free}

Y: year

WW: week

| Postfix | Package       |

|---------|---------------|

| S       | SOP (300 mil) |

| V       | LQFP          |

# **Features**

- Main Flash ROM 16KB, 128B/page

- Working voltage 1.8V~5.5V

- High speed architecture of 1 clock/machine cycle runs up to 25MHz.

- 256 bytes SRAM as standard 8052, plus 1K bytes on-chip expandable SRAM.

- Dual 16-bit Data Pointers (DPTR0 & DPTR1).

- One serial peripheral interfaces in full duplex mode (UART).

- Synchronous mode, fixed baud rate.

- 8-bit UART mode, variable baud rate.

- 9-bit UART mode, fixed baud rate.

- 9-bit UART mode, variable baud rate.

- Additional Baud Rate Generator for Serial port.

- Three 16-bit Timer/Counters. (Timer 0, 1, 2).

- Programmable watchdog timer.

- One IIC interface. (Master/Slave mode).

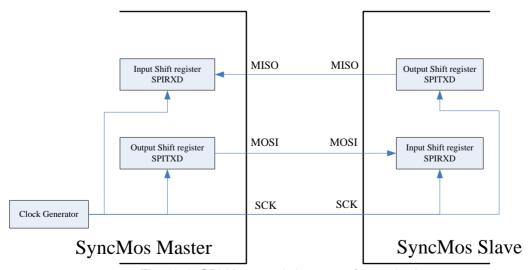

- One SPI interface. (Master/Slave mode)

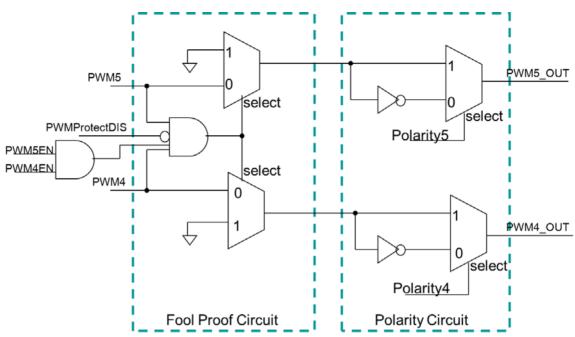

- 4-channel 14-bit PWM for motor control

- 4-channel 16-bit compare / capture / load functions.

- Comparator out can be CCU input source internally.

- Noise filter with CCU input with sample frequency select.

- ISP/IAP/ICP functions.

- EEPROM function.

- On-Chip in-circuit emulator (ICE) functions with On-Chip Debugger (OCD).

- Fast multiplication-division unit (MDU): 16\*16, 32/16, 16/16, 32-bit L/R shifting and 32-bit normalization.

- LVI/LVR (LVR deglitch 500ns).

- Enhance user code protection.

- Power management unit for IDLE and power down modes.

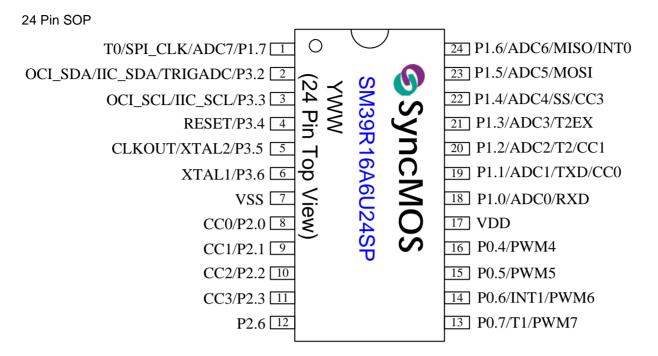

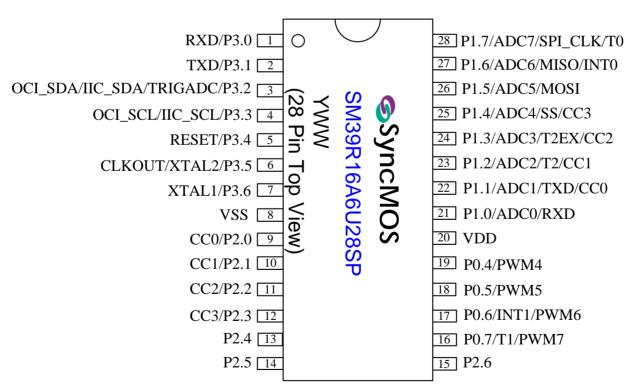

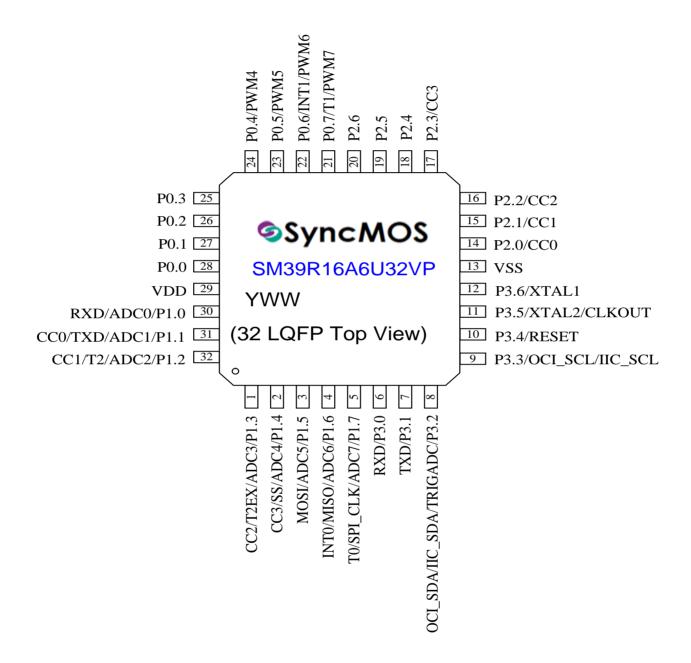

# **Pin Configuration**

28 Pin SOP

32 Pin LQFP

#### Notes:

- (1) The pin Reset/P3.4 factory default is GPIO (P3.4). User can configure it to reset by a flash programmer.

- (2) To avoid accidentally entering ISP-Mode(refer to section 18.4), care must be taken not asserting pulse signal at RXD P3.0 during power-up while P1.2, P1.3 or P1.4 are set to high.

- (3) To apply ICP function, OCI\_SDA/P3.2 and OCI\_SCL/P3.3 are ICP pins during reset period. When reset finish, they are GPIO.

# **Block Diagram**

# **Pin Description**

| 32L<br>LQFP | 28L<br>SOP | 24L<br>SOP | Symbol                           | I/O        | Description                                                                                                               |

|-------------|------------|------------|----------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| 1           | 24         | 21         | P1.3/ADC3/T2EX/<br>CC2           | I/O        | Bit 3 of port 1 & ADC input channel 3 & Timer 2 capture trigger & Timer 2 compare/capture Channel 2                       |

| 2           | 25         | 22         | P1.4/ADC4/SS/C<br>C3             | I/O        | Bit 4 of port 1 & ADC input channel 4 & SPI interface Slave Select pin & Timer 2 compare/capture Channel 3                |

| 3           | 26         | 23         | P1.5/ADC5/MOSI                   | I/O        | Bit 5 of port 1 & ADC input channel 5 & SPI interface Serial Data Master Output or Slave Input pin                        |

| 4           | 27         | 24         | P1.6/ADC6/MISO/<br>INT0          | I/O        | Bit 6 of port 1 & ADC input channel 6 & SPI interface Serial Data Master Input or Slave Output pin & External interrupt 0 |

| 5           | 28         | 1          | P1.7/ADC7/SPI_<br>CLK/T0         | I/O        | Bit 7 of port 1 & ADC input channel 7 & SPI interface Clock pin & Timer 0 external input                                  |

| 6           | 1          |            | P3.0/RXD                         | I/O        | Bit 0 of port 3 & Serial interface channel Receive data                                                                   |

| 7           | 2          |            | P3.1/TXD                         | I/O        | Bit 1 of port 3 & Serial interface channel Transmit data or receive clock in mode 0                                       |

| 8           | 3          | 2          | P3.2/TRIGADC/II<br>C_SDA/OCI_SDA | I/O        | Bit 2 of port 3 & external pin to trigger ADC & IIC SDA pin & On-Chip Instrumentation SDA                                 |

| 9           | 4          | 3          | P3.3/IIC_SCL/OC<br>I_SCL         | I/O        | Bit 3 of port 3 & IIC SCL pin & On-Chip Instrumentation SCL                                                               |

| 10          | 5          | 4          | P3.4/RESET                       | I/O        | Bit 4 of port 3 & Reset pin                                                                                               |

| 11          | 6          | 5          | P3.5/XTAL2/CLK<br>OUT            | I/O        | Bit 5 of port 3 & Crystal output & clock out                                                                              |

| 12          | 7          | 6          | P3.6/XTAL1                       | I/O        | Bit 6 of port 3 & Crystal input                                                                                           |

| 13          | 8          | 7          | VSS                              |            | Ground                                                                                                                    |

| 14          | 9          | 8          | P2.0/CC0                         | I/O        | Bit 0 of port 2 & Timer 2 compare/capture Channel 0                                                                       |

| 15          | 10         | 9          | P2.1/CC1                         | I/O        | Bit 1 of port 2 & Timer 2 compare/capture Channel 1                                                                       |

| 16          | 11         | 10         | P2.2/CC2                         | I/O        | Bit 2 of port 2 & Timer 2 compare/capture Channel 2                                                                       |

| 17          | 12         | 11         | P2.3/CC3                         | I/O        | Bit 3 of port 2 & Timer 2 compare/capture Channel 3                                                                       |

| 18          | 13         |            | P2.4                             | I/O        | Bit 4 of port 2                                                                                                           |

| 19          | 14         | 40         | P2.5                             | 1/0        | Bit 5 of port 2                                                                                                           |

| 20<br>21    | 15<br>16   | 12<br>13   | P2.6<br>P0.7/PWM7/T1             | I/O<br>I/O | Bit 6 of port 2                                                                                                           |

| 22          | 17         | 14         | P0.7/PWM7/11                     | 1/0        | Bit 7 of port 0 & PWM Channel 7 & Timer 1 external input Bit 6 of port 0 & PWM Channel 6 & External interrupt 1           |

| 23          | 18         | 15         | P0.5/PWM5                        | 1/0        | Bit 5 of port 0 & PWM Channel 5                                                                                           |

| 24          | 19         | 16         | P0.4/PWM4                        | I/O        | Bit 4 of port 0 & PWM Channel 4                                                                                           |

| 25          |            |            | P0.3                             | I/O        | Bit 3 of port 0                                                                                                           |

| 26          |            |            | P0.2                             | I/O        | Bit 2 of port 0                                                                                                           |

| 27          |            |            | P0.1                             | I/O        | Bit 1 of port 0                                                                                                           |

| 28          |            |            | P0.0                             | I/O        | Bit 0 of port 0                                                                                                           |

| 29          | 20         | 17         | VDD                              | I          | Power supply                                                                                                              |

| 30          | 21         | 18         | P1.0/ADC0/RXD                    | I/O        | Bit 0 of port 1 & ADC input channel 0 & Serial interface channel receive data                                             |

| 31          | 22         | 19         | P1.1/ADC1/TXD/<br>CC0            | I/O        | Bit 1 of port 1 & ADC input channel 1 & Serial interface channel Transmit data & Timer 2 compare/capture Channel 0        |

| 32          | 23         | 20         | P1.2/ADC2/T2/C<br>C1             | I/O        | Bit 2 of port 1 & ADC input channel 2 & Timer 2 external input clock & Timer 2 compare/capture Channel 1                  |

# **Special Function Register (SFR)**

A map of the Special Function Registers is shown as below:

#### In-direct access Mode

| HardDin | Vana  | V004   | V040        |             | V400   | V404   | V440        | V444   | Dis /Llass |

|---------|-------|--------|-------------|-------------|--------|--------|-------------|--------|------------|

| Hex\Bin | X000  | X001   | X010        | X011        | X100   | X101   | X110        | X111   | Bin/Hex    |

| F8      | IICS  | IICCTL | IICA1       | IICA2       | IICRWD | IICEBT |             |        | FF         |

| F0      | В     | SPIC1  | SPIC2       | SPITXD      | SPIRXD | SPIS   |             | TAKEY  | <b>F</b> 7 |

| E8      |       | MD0    | MD1         | MD2         | MD3    | MD4    | MD5         | ARCON  | EF         |

| E0      | ACC   | ISPFAH | ISPFAL      | ISPFD       | ISPFC  |        | LVC         | SWRES  | E7         |

| D8      |       | PFCON  | P3M0        | P3M1        |        |        |             |        | DF         |

| D0      | PSW   | CCEN2  | P0M0        | P0M1        | P1M0   | P1M1   | P2M0        | P2M1   | D7         |

| C8      | T2CON | CCCON  | CRCL        | CRCH        | TL2    | TH2    |             |        | CF         |

| C0      | IRCON | CCEN   | CCL1        | CCH1        | CCL2   | CCH2   | CCL3        | CCH3   | <b>C7</b>  |

| В8      | IEN1  | IP1    | SRELH       |             |        |        | PAGESE<br>L |        | BF         |

| В0      | P3    |        |             |             |        |        | WDTC        | WDTK   | B7         |

| A8      | IEN0  | IP0    | SRELL       | ADCC1       | ADCC2  | ADCDH  | ADCDL       | ADCCS  | AF         |

| A0      | P2    | RSTS   | PWM<br>ADDR | PWM<br>DATA |        |        |             |        | A7         |

| 98      | SCON  | SBUF   | IEN2        |             |        |        |             |        | 9F         |

| 90      | P1    | AUX    |             |             |        |        |             | IRCON2 | 97         |

| 88      | TCON  | TMOD   | TL0         | TL1         | TH0    | TH1    | CKCON       | IFCON  | 8F         |

| 80      | P0    | SP     | DPL         | DPH         | DPL1   | DPH1   | RCON        | PCON   | 87         |

| Hex\Bin | X000  | X001   | X010        | X011        | X100   | X101   | X110        | X111   | Bin/Hex    |

Page Mode: page0

| Hex\Bin | X000  | X001   | X010   | X011   | X100   | X101   | X110        | X111        | Bin/Hex   |

|---------|-------|--------|--------|--------|--------|--------|-------------|-------------|-----------|

| F8      | IICS  | IICCTL | IICA1  | IICA2  | IICRWD | IICEBT |             |             | FF        |

| F0      | В     | SPIC1  | SPIC2  | SPITXD | SPIRXD | SPIS   |             | TAKEY       | F7        |

| E8      |       | MD0    | MD1    | MD2    | MD3    | MD4    | MD5         | ARCON       | EF        |

| E0      | ACC   | ISPFAH | ISPFAL | ISPFD  | ISPFC  |        | LVC         | SWRES       | E7        |

| D8      |       | PFCON  | P3M0   | P3M1   |        |        |             |             | DF        |

| D0      | PSW   | CCEN2  | P0M0   | P0M1   | P1M0   | P1M1   | P2M0        | P2M1        | D7        |

| C8      | T2CON | CCCON  | CRCL   | CRCH   | TL2    | TH2    | OpPin2      | Cmp2CO<br>N | CF        |

| C0      | IRCON | CCEN   | CCL1   | CCH1   | CCL2   | CCH2   | CCL3        | CCH3        | <b>C7</b> |

| B8      | IEN1  | IP1    | SRELH  |        |        |        | PAGESE<br>L |             | BF        |

| В0      | P3    |        |        |        |        |        | WDTC        | WDTK        | B7        |

| A8      | IEN0  | IP0    | SRELL  | ADCC1  | ADCC2  | ADCDH  | ADCDL       | ADCCS       | AF        |

| A0      | P2    | RSTS   |        |        |        |        |             |             | A7        |

| 98      | SCON  | SBUF   | IEN2   |        |        |        |             |             | 9F        |

| 90      | P1    | AUX    |        |        |        |        |             | IRCON2      | 97        |

| 88      | TCON  | TMOD   | TL0    | TL1    | TH0    | TH1    | CKCON       | IFCON       | 8F        |

| 80      | P0    | SP     | DPL    | DPH    | DPL1   | DPH1   | RCON        | PCON        | 87        |

| Hex\Bin | X000  | X001   | X010   | X011   | X100   | X101   | X110        | X111        | Bin/Hex   |

Page Mode: page1

|         |       |         | 240.40  | 1 age Mot |        |        |         |        | - · · · ·  |

|---------|-------|---------|---------|-----------|--------|--------|---------|--------|------------|

| Hex\Bin | X000  | X001    | X010    | X011      | X100   | X101   | X110    | X111   | Bin/Hex    |

| F8      |       | PWMTBC  | PWMTBC  | PWMOP     |        |        |         |        | FF         |

| 10      |       | 0       | 1       | MOD       |        |        |         |        | • •        |

| F0      | В     | PERIODL | PERIODH |           |        | PWMEN  |         | TAKEY  | F7         |

|         |       |         |         |           |        |        | PWMTB   |        |            |

| E8      |       |         |         |           |        |        | POST    |        | EF         |

|         |       |         |         |           |        |        | SCALE   |        |            |

| E0      | ACC   | ISPFAH  | ISPFAL  | ISPFD     | ISPFC  |        | LVC     | SWRES  | E7         |

| D8      |       | PFCON   |         |           |        | PWMPOL |         |        | DF         |

|         |       | 11001   |         |           |        | ARITY  |         |        | <b>D</b> 1 |

| D0      | PSW   |         |         |           |        | DUTY2L | DUTY2H  | DUTY3L | D7         |

| C8      | T2CON | DUTY3H  |         |           | TL2    | TH2    |         |        | CF         |

| C0      | IRCON |         |         |           |        |        |         |        | <b>C7</b>  |

| В8      | IEN1  | IP1     | SRELH   |           | PWMINT |        | PAGESEL |        | BF         |

| - D0    | Do    |         |         |           | F      |        |         | MOTIC  | D-7        |

| В0      | P3    |         |         |           |        |        | WDTC    | WDTK   | B7         |

| A8      | IEN0  | IP0     | SRELL   | ADCC1     | ADCC2  | ADCDH  | ADCDL   | ADCCS  | AF         |

| A0      | P2    |         |         |           |        |        |         |        | A7         |

| 98      | SCON  | SBUF    | IEN2    |           |        |        |         |        | 9F         |

| 90      | P1    | AUX     |         |           |        |        |         | IRCON2 | 97         |

| 88      | TCON  | TMOD    | TL0     | TL1       | TH0    | TH1    | CKCON   | IFCON  | 8F         |

| 80      | P0    | SP      | DPL     | DPH       | DPL1   | DPH1   | RCON    | PCON   | 87         |

| Hex\Bin | X000  | X001    | X010    | X011      | X100   | X101   | X110    | X111   | Bin/Hex    |

Note: Special Function Registers reset values and description for SM39R16A6.

|          | Loc      | ation: 80h ~       | 8Fh       | Reset   |                                         |  |

|----------|----------|--------------------|-----------|---------|-----------------------------------------|--|

| Register | Method 1 | Method 2<br>Page 0 |           |         | Description                             |  |

|          |          |                    | SYSTEM    |         |                                         |  |

| SP       | 81h      | 81h                | 81h       | 07h     | Stack Pointer                           |  |

| ACC      | E0h      | E0h                | E0h       | 00h     | Accumulator                             |  |

| PSW      | D0h      | D0h                | D0h       | 00h     | Program Status Word                     |  |

| В        | F0h      | F0h                | F0h       | 00h     | B Register                              |  |

| DPL      | 82h      | 82h                | 82h       | 00h     | Data Pointer 0 low byte                 |  |

| DPH      | 83h      | 83h                | 83h       | 00h     | Data Pointer 0 high byte                |  |

| DPL1     | 84h      | 84h                | 84h       | 00h     | Data Pointer 1 low byte                 |  |

| DPH1     | 85h      | 85h                | 85h       | 00h     | Data Pointer 1 high byte                |  |

| AUX      | 91h      | 91h                | 91h       | 00h     | Auxiliary register                      |  |

| PCON     | 87h      | 87h                | 87h       | 40h     | Power Control                           |  |

| CKCON    | 8Eh      | 8Eh                | 8Eh       | 10h     | Clock control register                  |  |

| PAGESEL  | BEh      | BEh                | BEh       | 00h     | Page select                             |  |

|          | <u>-</u> | INTE               | RRUPT & P | RIORITY |                                         |  |

| IRCON    | C0h      | C0h                | C0h       | 00h     | Interrupt Request Control Register      |  |

| IRCON2   | 97h      | 97h                | 97h       | 00h     | Interrupt Request Control Register 2    |  |

| IEN0     | A8h      | A8h                | A8h       | 00h     | Interrupt Enable Register 0             |  |

| IEN1     | B8h      | B8h                | B8h       | 00h     | Interrupt Enable Register 1             |  |

| IEN2     | 9Ah      | 9Ah                | 9Ah       | 00h     | Interrupt Enable Register 2             |  |

| IP0      | A9h      | A9h                | A9h       | 00h     | Interrupt Priority Register 0           |  |

| IP1      | B9h      | B9h                | B9h       | 00h     | Interrupt Priority Register 1           |  |

|          | <u> </u> | <u> </u>           | UART      |         |                                         |  |

| PCON     | 87h      | 87h                | 87h       | 40h     | Power Control                           |  |

| AUX      | 91h      | 91h                | 91h       | 00h     | Auxiliary register                      |  |

| SCON     | 98h      | 98h                | 98h       | 00h     | Serial Port, Control Register           |  |

| SBUF     | 99h      | 99h                | 99h       | 00h     | Serial Port, Data Buffer                |  |

| SRELL    | AAh      | AAh                | AAh       | 00h     | Serial Port, Reload Register, low byte  |  |

| SRELH    | BAh      | BAh                | BAh       | 00h     | Serial Port, Reload Register, high byte |  |

| PFCON    | D9h      | D9h                | D9h       | 00h     | Peripheral Frequency control register   |  |

|          | - 4      | <u> </u>           | ADC       |         |                                         |  |

| ADCC1    | ABh      | ABh                | ABh       | 00h     | ADC Control 1 Register                  |  |

| ADCC2    | ACh      | ACh                | ACh       | 08h     | ADC Control 2 Register                  |  |

| ADCDH    | ADh      | ADh                | ADh       | 00h     | ADC data high byte                      |  |

| ADCDL    | AEh      | AEh                | AEh       | 00h     | ADC data low byte                       |  |

| ADCCS    |          |                    | AFh       | 00h     | ADC clock select                        |  |

|          | <u> </u> |                    | WDT       |         | !                                       |  |

| RSTS     | A1h      | A1h                |           | 00h     | Reset status register                   |  |

| WDTC     | B6h      | B6h                | B6h       | 04h     | Watchdog timer control register         |  |

|          |          |                    |           | -       | 1                                       |  |

|                    | Location: 80h ~ |                    | 8Fh                | Reset |                                           |

|--------------------|-----------------|--------------------|--------------------|-------|-------------------------------------------|

| Register           | Method 1        | Method 2<br>Page 0 | Method 2<br>Page 1 | value | Description                               |

| WDTK               | B7h             | B7h                | B7h                | 00h   | Watchdog timer refresh key.               |

| TAKEY              | F7h             | F7h                | F7h                | 00h   | Time Access Key register                  |

|                    |                 |                    | PWM                |       |                                           |

| PWMTBC0            |                 |                    | F9h                | 00h   | PWM Time Base Control 0 Reg.              |

| PWMTBC1            |                 |                    | FAh                | 10h   | PWM Time Base Control 1 Reg.              |

| PWMOPMOD           |                 |                    | FBh                | 00h   | PWM Output Pair Mode Reg.                 |

| PERIODL            |                 |                    | F1h                | FFh   | PWM Period (Low) Reg.                     |

| PERIODH            |                 |                    | F2h                | 3Fh   | PWM Period (High) Reg.                    |

| PWMEN              |                 |                    | F5h                | 00h   | PWM Output Enable Reg.                    |

| PWMTBPOST<br>SCALE |                 |                    | EEh                | 00h   | PWM Time Base Post Scale Reg.             |

| PWMINTF            |                 |                    | BCh                | 00h   | PWM INT Flag Reg.                         |

| PWMPOLARITY        |                 |                    | DDh                | FFh   | PWM Polarity Reg.                         |

| DUTY2L             |                 |                    | D5h                | 00h   | PWM 2 Duty Low byte Reg.                  |

| DUTY2H             |                 |                    | D6h                | 00h   | PWM 2 Duty High byte Reg.                 |

| DUTY3L             |                 |                    | D7h                | 00h   | PWM 3 Duty Low byte Reg.                  |

| DUTY3H             |                 |                    | C9h                | 00h   | PWM 3 Duty High byte Reg.                 |

| PWMADDR            | A2h             |                    |                    | 00h   | PWM Address Register                      |

| PWMDATA            | A3h             |                    |                    | 00h   | PWM Data Register                         |

|                    | -               |                    | TIMER0/TIM         | ER1   |                                           |

| TCON               | 88h             | 88h                | 88h                | 00h   | Timer/Counter Control                     |

| TMOD               | 89h             | 89h                | 89h                | 00h   | Timer Mode Control                        |

| TL0                | 8Ah             | 8Ah                | 8Ah                | 00h   | Timer 0, low byte                         |

| TL1                | 8Bh             | 8Bh                | 8Bh                | 00h   | Timer 1, low byte                         |

| TH0                | 8Ch             | 8Ch                | 8Ch                | 00h   | Timer 0, high byte                        |

| TH1                | 8Dh             | 8Dh                | 8Dh                | 00h   | Timer 1, high byte                        |

| PFCON              | D9h             | D9h                | D9h                | 00h   | Peripheral Frequency control register     |

|                    | <del>-</del>    |                    | PCA(TIME           | R2)   | •                                         |

| CCEN               | C1h             | C1h                |                    | 00h   | Compare/Capture Enable Register           |

| CCL1               | C2h             | C2h                |                    | 00h   | Compare/Capture Register 1, low byte      |

| CCH1               | C3h             | C3h                |                    | 00h   | Compare/Capture Register 1, high byte     |

| CCL2               | C4h             | C4h                |                    | 00h   | Compare/Capture Register 2, low byte      |

| CCH2               | C5h             | C5h                |                    | 00h   | Compare/Capture Register 2, high byte     |

| CCL3               | C6h             | C6h                |                    | 00h   | Compare/Capture Register 3, low byte      |

| ССН3               | C7h             | C7h                |                    | 00h   | Compare/Capture Register 3, high byte     |

| T2CON              | C8h             | C8h                | C8h                | 00h   | Timer 2 Control                           |

| CCCON              | C9h             | C9h                |                    | 00h   | Compare/Capture Control                   |

| CRCL               | CAh             | CAh                |                    | 00h   | Compare/Reload/Capture Register, low byte |

|          | Location: 80h ~ 8F |                    | 8Fh                | Danet          |                                            |

|----------|--------------------|--------------------|--------------------|----------------|--------------------------------------------|

| Register | Method 1           | Method 2<br>Page 0 | Method 2<br>Page 1 | Reset<br>value | Description                                |

| CRCH     | CBh                | CBh                |                    | 00h            | Compare/Reload/Capture Register, high byte |

| TL2      | CCh                | CCh                | CCh                | 00h            | Timer 2, low byte                          |

| TH2      | CDh                | CDh                | CDh                | 00h            | Timer 2, high byte                         |

| CCEN2    | D1h                | D1h                |                    | 00h            | Compare/Capture Enable 2 register          |

|          | -                  |                    | GPIO               |                |                                            |

| P0       | 80h                | 80h                | 80h                | User<br>define | Port 0                                     |

| P1       | 90h                | 90h                | 90h                | FFh            | Port 1                                     |

| P2       | A0h                | A0h                | A0h                | 7Fh            | Port 2                                     |

| P3       | B0h                | B0h                | B0h                | 7Fh            | Port 3                                     |

| P0M0     | D2h                | D2h                |                    | User<br>define | Port 0 output mode 0                       |

| P0M1     | D3h                | D3h                |                    | 00h            | Port 0 output mode 1                       |

| P1M0     | D4h                | D4h                |                    | 00h            | Port 1 output mode 0                       |

| P1M1     | D5h                | D5h                |                    | 00h            | Port 1 output mode 1                       |

| P2M0     | D6h                | D6h                |                    | 00h            | Port 2 output mode 0                       |

| P2M1     | D7h                | D7h                |                    | 00h            | Port 2 output mode 1                       |

| P3M0     | DAh                | DAh                |                    | 00h            | Port 3 output mode 0                       |

| P3M1     | DBh                | DBh                |                    | 00h            | Port 3 output mode 1                       |

|          |                    | l                  | SP/IAP/EEPI        | ROM            |                                            |

| IFCON    | 8Fh                | 8Fh                | 8Fh                | 00h            | Interface control register                 |

| ISPFAH   | E1h                | E1h                | E1h                | FFh            | ISP Flash Address-High register            |

| ISPFAL   | E2h                | E2h                | E2h                | FFh            | ISP Flash Address-Low register             |

| ISPFD    | E3h                | E3h                | E3h                | FFh            | ISP Flash Data register                    |

| ISPFC    | E4h                | E4h                | E4h                | 00h            | ISP Flash control register                 |

| TAKEY    | F7h                | F7h                | F7h                | 00h            | Time Access Key register                   |

|          |                    | LV                 | I/LVR/SOFTI        | RESET          |                                            |

| RSTS     | A1h                | A1h                |                    | 00h            | Reset status register                      |

| LVC      | E6h                | E6h                | E6h                | 20h            | Low voltage control register               |

| SWRES    | E7h                | E7h                | E7h                | 00h            | Software Reset register                    |

| TAKEY    | F7h                | F7h                | F7h                | 00h            | Time Access Key register                   |

|          |                    |                    | SPI                |                |                                            |

| SPIC1    | F1h                | F1h                |                    | 08h            | SPI control register 1                     |

| SPIC2    | F2h                | F2h                |                    | 00h            | SPI control register 2                     |

| SPITXD   | SPITXD F3h         |                    |                    | 00h            | SPI Transmit data buffer                   |

| SPIRXD   | F4h                | F4h                |                    | 00h            | SPI receive data buffer                    |

| SPIS     | SPIS F5h F5h       |                    |                    | 40h            | SPI status register                        |

|          |                    |                    | IIC                |                |                                            |

| IICS     | F8h                | F8h                |                    | 00h            | IIC status register                        |

| IICCTL   | F9h                | F9h                |                    | 04h            | IIC control register                       |

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M079

Ver D SM39R16A6 06/30/2015

|          | Loc         | ation: 80h ~       | 8Fh                | Reset |                                        |  |  |

|----------|-------------|--------------------|--------------------|-------|----------------------------------------|--|--|

| Register | Method 1    | Method 2<br>Page 0 | Method 2<br>Page 1 | value | Description                            |  |  |

| IICA1    | FAh         | FAh FAh<br>FBh FBh |                    | A0h   | IIC channel 1 Address 1 register       |  |  |

| IICA2    | FBh         |                    |                    | 60h   | IIC channel 1 Address 2 register       |  |  |

| IICRWD   | FCh FCh FDh |                    |                    | 00h   | IIC channel 1 Read / Write Data buffer |  |  |

| IICEBT   |             |                    |                    | 00h   | IIC Enable Bus Transaction register    |  |  |

# **Function Description**

#### 1. General Features

SM39R16A6 is an 8-bit micro-controller. All of its functions and the detailed meanings of SFR will be given in the following sections.

#### 1.1 Embedded Flash

The program can be loaded into the embedded 16KB Flash memory via its writer or In-System Programming (ISP). The high-quality Flash suitable for re-programming and data recording as EEPROM.

#### 1.2 IO Pads

The SM39R16A6 has Four I/O ports: Port 0, Port 1, Port 2 and Port 3. Ports 0, 1 are 8-bit ports and Port 2, 3 are 7-bit ports. These are: quasi-bidirectional (standard 8051 port outputs), push-pull, open drain, and input-only. As description in section 5.

All the pads for P0, P1, P2 and P3 are with slew rate to reduce EMI. The IO pads can withstand 4KV ESD in human body mode guaranteeing the SM39R16A6's quality in high electro-static environments.

The RESET Pin can define as General I/O P3.4 when user use Internal RESET.

The XTAL2 and XTAL1 can define as P3.5 and P3.6 by writer or ISP when user use internal OSC as system clock. When user use external OSC as system clock and input into XTAL1, only XTAL2 can be defined as P3.5.

#### 1.3 Instruction timing Selection

The conventional 52-series MCUs are 12T, i.e., 12 oscillator clocks per machine cycle. SM39R16A6 is a 1T to 8T MCU, i.e., its machine cycle is one-clock to eight-clock. In the other words, it can execute one instruction within one clock to only eight clocks.

| Mnemonic: CKCON Address: |   |          |   |   |   |      |         |       |

|--------------------------|---|----------|---|---|---|------|---------|-------|

| 7                        | 6 | 5        | 4 | 3 | 2 | 1    | 0       | Reset |

| -                        |   | ITS[2:0] |   | - | - | CLKO | UT[1:0] | 10H   |

ITS: Instruction timing select.

| ITS [2:0] | Instruction timing |

|-----------|--------------------|

| 000       | 1T mode            |

| 001       | 2T mode (default)  |

| 010       | 3T mode            |

| 011       | 4T mode            |

| 100       | 5T mode            |

| 101       | 6T mode            |

| 110       | 7T mode            |

| 111       | 8T mode            |

The default is in 2T mode, and it can be changed to another Instruction timing mode if CKCON [6:4] (at address 8Eh) is change any time. Not every instruction can be executed with one machine cycle. The exact machine cycle number for all the instructions are given in the next section.

#### 1.4 Clock Out Selection

The SM39R16A6 can generate a clock out signal at P3.5 when user use Oscillator (XTAL1 as clock input) or internal OSC as system clock. The CKCON [1:0] (at address 8Eh) can change any time.

CLKOUT: Clock output select.

| CKCON [1:0] | Mode.         |

|-------------|---------------|

| 00          | GPIO(default) |

| 01          | Fosc          |

| 10          | Fosc/2        |

| 11          | Fosc/4        |

#### 1.5 RESET

#### 1.5.1 Hardware RESET function

SM39R16A6 provides Internal reset circuit inside, the Internal reset time can set by writer or ISP.

| Internal Reset time |  |  |  |  |  |

|---------------------|--|--|--|--|--|

| 25ms (default)      |  |  |  |  |  |

| 200ms               |  |  |  |  |  |

| 100ms               |  |  |  |  |  |

| 50ms                |  |  |  |  |  |

| 16ms                |  |  |  |  |  |

| 8ms                 |  |  |  |  |  |

| 4ms                 |  |  |  |  |  |

#### 1.5.2 Software RESET function

SM39R16A6 provides one software reset mechanism to reset whole chip. To perform a software reset, the firmware must write three specific values 55h, AAh and 5Ah sequentially to the TAKEY register to enable the Software Reset register (SWRES) write attribute. After SWRES register obtain the write authority, the firmware can write FFh to the SWRES register. The hardware will decode a reset signal that "OR" with the other hardware reset. The SWRES register is self-reset at the end of the software reset procedure.

| Mnemonic                | Description                 | Dir. | Bit 7 | Bit 6                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | RST |

|-------------------------|-----------------------------|------|-------|----------------------------------------|-------|-------|-------|-------|-------|-------|-----|

| Software Reset function |                             |      |       |                                        |       |       |       |       |       |       |     |

| RSTS                    | Reset status register       | A1h  | -     | - LVRLP LVRLP PDRF WDTF SWRF LVRF PORF |       |       |       | 00H   |       |       |     |

| TAKEY                   | Time Access<br>Key register | F7h  |       | TAKEY [7:0]                            |       |       |       | 00H   |       |       |     |

| SWRES                   | Software Reset register     | E7h  |       | SWRES [7:0]                            |       |       | 00H   |       |       |       |     |

#### 1.5.3 Reset status

Mnemonic: RSTS Address: A1h 5 4 3 2 Reset 6 LVRLP **LVRLPF** PDRF WDTF **SWRF** I VRF PORF 00H INTF

LVRLPINTF: "Internal" Low voltage reset flag.

When MCU is reset by LVR\_LP\_INT, LVRLPINTF flag will be set to one by hardware. This flag clear by software.

LVRLPF: Low voltage reset (Low Power) flag.

When MCU is reset by LVR (Low Power), LVRLPF flag will be set to one by hardware. This flag clear by software.

PDRF: Pad reset flag.

When MCU is reset by reset pad, PDRF flag will be set to one by hardware. This flag clear by software.

WDTF: Watchdog timer reset flag.

When MCU is reset by watchdog, WDTF flag will be set to one by hardware. This flag clear by software.

SWRF: Software reset flag.

When MCU is reset by software, SWRF flag will be set to one by hardware. This flag clear by software.

LVRF: Low voltage reset flag.

When MCU is reset by LVR, LVRF flag will be set to one by hardware. This flag clear by software.

PORF: Power on reset flag.

When MCU is reset by POR, PORF flag will be set to one by hardware. This flag clear by software.

# 1.5.4 Time Access Key register (TAKEY)

| Mnemor | nic: TAKE | Y |      |         |   |   | Add | ress:F7H |

|--------|-----------|---|------|---------|---|---|-----|----------|

| 7      | 6         | 5 | 4    | 3       | 2 | 1 | 0   | Reset    |

|        |           |   | TAKE | Y [7:0] |   |   |     | 00H      |

Software reset register (SWRES) is read-only by default, software must write three specific values 55h, AAh and 5Ah sequentially to the TAKEY register to enable the SWRES register write attribute.

That is:

MOV TAKEY, #55h MOV TAKEY, #0AAh MOV TAKEY, #5Ah

# 1.5.5 Software Reset register (SWRES)

Mnemonic: SWRES

Address:E7H

7

6

5

4

3

2

1

0

Reset

SWRES [7:0]

00H

SWRES [7:0]: Software reset register bit. These 8-bit is self-reset at the end of the reset procedure.

SWRES [7:0] = FFh, software reset.

SWRES  $[7:0] = 00h \sim FEh$ , MCU no action.

## 1.5.6 Example of software reset

MOV TAKEY, #55h MOV TAKEY, #0AAh

MOV TAKEY, #5Ah ; enable SWRES write attribute

MOV SWRES, #0FFh; software reset MCU

#### 1.6 Clocks

The default clock is the 22.1184MHz Internal OSC. This clock is used during the initialization stage. The major work of the initialization stage is to determine the clock source used in normal operation.

The internal clock sources are from the internal OSC with difference frequency division As shown in Table 1-1, the clock source can set by writer.

Table 1-1: Selection of clock source

| Clock source                                               |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|

| external crystal (use XTAL1 and XTAL2 pins )               |  |  |  |  |

| external crystal (only use XTAL1, the XTAL2 define as I/O) |  |  |  |  |

| 22.1184MHz from internal OSC                               |  |  |  |  |

| 11.0592MHz from internal OSC                               |  |  |  |  |

| 5.5296MHz from internal OSC                                |  |  |  |  |

| 2.7648MHz from internal OSC                                |  |  |  |  |

| 1.3824MHz from internal OSC                                |  |  |  |  |

There may be having a little variance in the frequency from the internal OSC. The max variance as giving in Table 1-2.

Table 1-2: Temperature with variance

| Temperature | Max Variance |

|-------------|--------------|

| <b>25</b> ℃ | ±2%          |

# 2. Instruction Set

All SM39R16A6 instructions are binary code compatible and perform the same functions as they do with the industry standard 8051. The following tables give a summary of the instruction set cycles of the SM39R16A6 Microcontroller core.

Table 2-1: Arithmetic operations

| Mnemonic      | Description                                 | Code  | Bytes | Cycles |

|---------------|---------------------------------------------|-------|-------|--------|

| ADD A,Rn      | Add register to accumulator                 | 28-2F | 1     | 1      |

| ADD A,direct  | Add direct byte to accumulator              | 25    | 2     | 2      |

| ADD A,@Ri     | Add indirect RAM to accumulator             | 26-27 | 1     | 2      |

| ADD A,#data   | Add immediate data to accumulator           | 24    | 2     | 2      |

| ADDC A,Rn     | Add register to accumulator with carry flag | 38-3F | 1     | 1      |

| ADDC A,direct | Add direct byte to A with carry flag        | 35    | 2     | 2      |

| ADDC A,@Ri    | Add indirect RAM to A with carry flag       | 36-37 | 1     | 2      |

| ADDC A,#data  | Add immediate data to A with carry flag     | 34    | 2     | 2      |

| SUBB A,Rn     | Subtract register from A with borrow        | 98-9F | 1     | 1      |

| SUBB A,direct | Subtract direct byte from A with borrow     | 95    | 2     | 2      |

| SUBB A,@Ri    | Subtract indirect RAM from A with borrow    | 96-97 | 1     | 2      |

| SUBB A,#data  | Subtract immediate data from A with borrow  | 94    | 2     | 2      |

| INC A         | Increment accumulator                       | 04    | 1     | 1      |

| INC Rn        | Increment register                          | 08-0F | 1     | 2      |

| INC direct    | Increment direct byte                       | 05    | 2     | 3      |

| INC @Ri       | Increment indirect RAM                      | 06-07 | 1     | 3      |

| INC DPTR      | Increment data pointer                      | A3    | 1     | 1      |

| DEC A         | Decrement accumulator                       | 14    | 1     | 1      |

| DEC Rn        | Decrement register                          | 18-1F | 1     | 2      |

| DEC direct    | Decrement direct byte                       | 15    | 2     | 3      |

| DEC @Ri       | Decrement indirect RAM                      | 16-17 | 1     | 3      |

| MUL AB        | Multiply A and B                            | A4    | 1     | 5      |

| DIV           | Divide A by B                               | 84    | 1     | 5      |

| DA A          | Decimal adjust accumulator                  | D4    | 1     | 1      |

Table 2-2: Logic operations

| Mnemonic         | Description                                | Code  | Bytes | Cycles |

|------------------|--------------------------------------------|-------|-------|--------|

| ANL A,Rn         | AND register to accumulator                | 58-5F | 1     | 1      |

| ANL A,direct     | AND direct byte to accumulator             | 55    | 2     | 2      |

| ANL A,@Ri        | AND indirect RAM to accumulator            | 56-57 | 1     | 2      |

| ANL A,#data      | AND immediate data to accumulator          | 54    | 2     | 2      |

| ANL direct,A     | AND accumulator to direct byte             | 52    | 2     | 3      |

| ANL direct,#data | AND immediate data to direct byte          | 53    | 3     | 4      |

| ORL A,Rn         | OR register to accumulator                 | 48-4F | 1     | 1      |

| ORL A, direct    | OR direct byte to accumulator              | 45    | 2     | 2      |

| ORL A,@Ri        | OR indirect RAM to accumulator             | 46-47 | 1     | 2      |

| ORL A,#data      | OR immediate data to accumulator           | 44    | 2     | 2      |

| ORL direct,A     | OR accumulator to direct byte              | 42    | 2     | 3      |

| ORL direct,#data | OR immediate data to direct byte           | 43    | 3     | 4      |

| XRL A,Rn         | Exclusive OR register to accumulator       | 68-6F | 1     | 1      |

| XRL A,direct     | Exclusive OR direct byte to accumulator    | 65    | 2     | 2      |

| XRL A,@Ri        | Exclusive OR indirect RAM to accumulator   | 66-67 | 1     | 2      |

| XRL A,#data      | Exclusive OR immediate data to accumulator | 64    | 2     | 2      |

| XRL direct,A     | Exclusive OR accumulator to direct byte    | 62    | 2     | 3      |

| XRL direct,#data | Exclusive OR immediate data to direct byte | 63    | 3     | 4      |

| CLR A            | Clear accumulator                          | E4    | 1     | 1      |

| CPL A            | Complement accumulator                     | F4    | 1     | 1      |

| RL A             | Rotate accumulator left                    | 23    | 1     | 1      |

| RLC A            | Rotate accumulator left through carry      | 33    | 1     | 1      |

| RR A             | Rotate accumulator right                   | 03    | 1     | 1      |

| RRC A            | Rotate accumulator right through carry     | 13    | 1     | 1      |

| SWAP A           | Swap nibbles within the accumulator        | C4    | 1     | 1      |

|                  |                                            |       |       |        |

## Table 2-3: Data transfer

| Mnemonic             | Description                                    | Code  | Bytes | Cycles |

|----------------------|------------------------------------------------|-------|-------|--------|

| MOV A,Rn             | Move register to accumulator                   | E8-EF | 1     | 1      |

| MOV A,direct         | Move direct byte to accumulator                | E5    | 2     | 2      |

| MOV A,@Ri            | Move indirect RAM to accumulator               | E6-E7 | 1     | 2      |

| MOV A,#data          | Move immediate data to accumulator             | 74    | 2     | 2      |

| MOV Rn,A             | Move accumulator to register                   | F8-FF | 1     | 2      |

| MOV Rn,direct        | Move direct byte to register                   | A8-AF | 2     | 4      |

| MOV Rn,#data         | Move immediate data to register                | 78-7F | 2     | 2      |

| MOV direct,A         | Move accumulator to direct byte                | F5    | 2     | 3      |

| MOV direct,Rn        | Move register to direct byte                   | 88-8F | 2     | 3      |

| MOV direct1, direct2 | Move direct byte to direct byte                | 85    | 3     | 4      |

| MOV direct,@Ri       | Move indirect RAM to direct byte               | 86-87 | 2     | 4      |

| MOV direct,#data     | Move immediate data to direct byte             | 75    | 3     | 3      |

| MOV @Ri,A            | Move accumulator to indirect RAM               | F6-F7 | 1     | 3      |

| MOV @Ri,direct       | Move direct byte to indirect RAM               | A6-A7 | 2     | 5      |

| MOV @Ri,#data        | Move immediate data to indirect RAM            | 76-77 | 2     | 3      |

| MOV DPTR,#data16     | Load data pointer with a 16-bit constant       | 90    | 3     | 3      |

| MOVC A,@A+DPTR       | Move code byte relative to DPTR to accumulator | 93    | 1     | 3      |

| MOVC A,@A+PC         | Move code byte relative to PC to accumulator   | 83    | 1     | 3      |

| MOVX A,@Ri           | Move external RAM (8-bit addr.) to A           | E2-E3 | 1     | 3      |

| MOVX A,@DPTR         | Move external RAM (16-bit addr.) to A          | E0    | 1     | 3      |

| MOVX @Ri,A           | Move A to external RAM (8-bit addr.)           | F2-F3 | 1     | 4      |

| MOVX @DPTR,A         | Move A to external RAM (16-bit addr.)          | F0    | 1     | 4      |

| PUSH direct          | Push direct byte onto stack                    | C0    | 2     | 4      |

| POP direct           | Pop direct byte from stack                     | D0    | 2     | 3      |

| XCH A,Rn             | Exchange register with accumulator             | C8-CF | 1     | 2      |

| XCH A,direct         | Exchange direct byte with accumulator          | C5    | 2     | 3      |

| XCH A,@Ri            | Exchange indirect RAM with accumulator         | C6-C7 | 1     | 3      |

| XCHD A,@Ri           | Exchange low-order nibble indir. RAM with A    | D6-D7 | 1     | 3      |

Table 2-4: Program branches

| Mnemonic           | Description                                    | Code  | Bytes | Cycles |

|--------------------|------------------------------------------------|-------|-------|--------|

| ACALL addr11       | Absolute subroutine call                       | xxx11 | 2     | 6      |

| LCALL addr16       | Long subroutine call                           | 12    | 3     | 6      |

| RET                | from subroutine                                | 22    | 1     | 4      |

| RETI               | from interrupt                                 | 32    | 1     | 4      |

| AJMP addr11        | Absolute jump                                  | xxx01 | 2     | 3      |

| LJMP addr16        | Long iump                                      | 02    | 3     | 4      |

| SJMP rel           | Short jump (relative addr.)                    | 80    | 2     | 3      |

| JMP @A+DPTR        | Jump indirect relative to the DPTR             | 73    | 1     | 2      |

| JZ rel             | Jump if accumulator is zero                    | 60    | 2     | 3      |

| JNZ rel            | Jump if accumulator is not zero                | 70    | 2     | 3      |

| JC rel             | Jump if carry flag is set                      | 40    | 2     | 3      |

| JNC                | Jump if carry flag is not set                  | 50    | 2     | 3      |

| JB bit,rel         | Jump if direct bit is set                      | 20    | 3     | 4      |

| JNB bit,rel        | Jump if direct bit is not set                  | 30    | 3     | 4      |

| JBC bit,direct rel | Jump if direct bit is set and clear bit        | 10    | 3     | 4      |

| CJNE A,direct rel  | Compare direct byte to A and jump if not equal | B5    | 3     | 4      |

| CJNE A,#data rel   | Compare immediate to A and jump if not equal   | B4    | 3     | 4      |

| CJNE Rn,#data rel  | Compare immed. to reg. and jump if not equal   | B8-BF | 3     | 4      |

| CJNE @Ri,#data rel | Compare immed. to ind. and jump if not equal   | B6-B7 | 3     | 4      |

| DJNZ Rn,rel        | Decrement register and jump if not zero        | D8-DF | 2     | 3      |

| DJNZ direct,rel    | Decrement direct byte and jump if not zero     | D5    | 3     | 4      |

| NOP                | No operation                                   | 00    | 1     | 1      |

Table 2-5: Boolean manipulation

| Mnemonic   | Description                           | Code | Bytes | Cycles |

|------------|---------------------------------------|------|-------|--------|

| CLR C      | Clear carry flag                      | C3   | 1     | 1      |

| CLR bit    | Clear direct bit                      | C2   | 2     | 3      |

| SETB C     | Set carry flag                        | D3   | 1     | 1      |

| SETB bit   | Set direct bit                        | D2   | 2     | 3      |

| CPL C      | Complement carry flag                 | B3   | 1     | 1      |

| CPL bit    | Complement direct bit                 | B2   | 2     | 3      |

| ANL C,bit  | AND direct bit to carry flag          | 82   | 2     | 2      |

| ANL C,/bit | AND complement of direct bit to carry | B0   | 2     | 2      |

| ORL C,bit  | OR direct bit to carry flag           | 72   | 2     | 2      |

| ORL C,/bit | OR complement of direct bit to carry  | A0   | 2     | 2      |

| MOV C,bit  | Move direct bit to carry flag         | A2   | 2     | 2      |

| MOV bit,C  | Move carry flag to direct bit         | 92   | 2     | 3      |

# 3. Memory Structure

The SM39R16A6 memory structure follows general 8052 structure. It is integrate the expanded 1KB data memory and 16KB program memory.

### 3.1 Program Memory

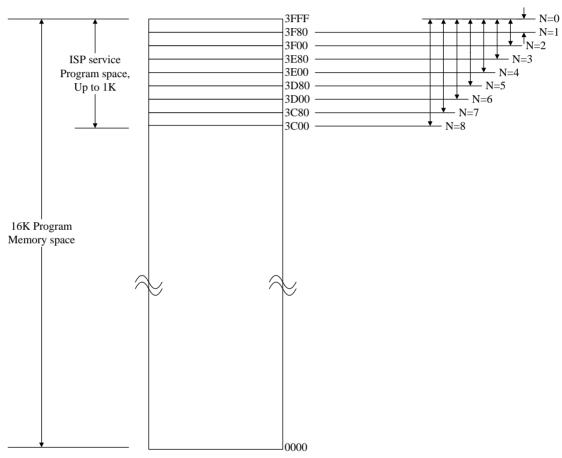

The SM39R16A6 has 16KB on-chip flash memory which can be used as general program memory or EEPROM, on which include up to 1K byte specific ISP service program memory space. The address range for the 16K byte is \$0000 to \$3FFF. The address range for the ISP service program is \$3C00 to \$3FFF. The ISP service program size can be partitioned as N blocks of 128 byte (N=0 to 8). When N=0 means no ISP service program space available, total 16K byte memory used as program memory. When N=1 means address \$3F80 to \$3FFF reserved for ISP service program. When N=2 means memory address \$3F00 to \$3FFF reserved for ISP service program...etc. Value N can be set and programmed into SM39R16A6 information block by writer. As shown in Fig. 3-1

Fig. 3-1: SM39R16A6 programmable Flash

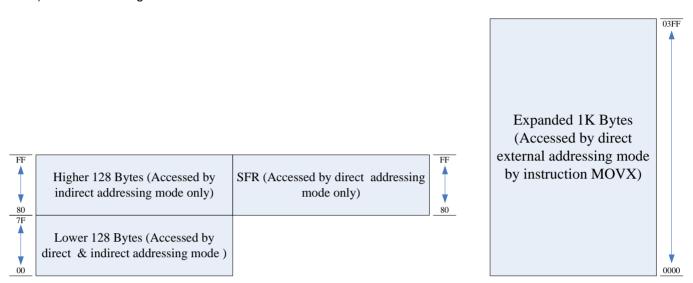

# 3.2 Data Memory

The SM39R16A6 has 1K + 256B on-chip SRAM, 256B of it are the same as general 8052 internal memory structure while the expanded 1K Bytes on-chip SRAM can be accessed by external memory addressing method (by instruction MOVX.). As shown in Fig. 3-2

Fig. 3-2: RAM architecture

# 3.3 Data memory - lower 128 byte (00h to 7Fh)

Data memory 00h to FFh is the same as 8052.

The address 00h to 7Fh can be accessed by direct and indirect addressing modes.

Address 00h to 1Fh is register area.

Address 20h to 2Fh is memory bit area.

Address 30h to 7Fh is for general memory area.

# 3.4 Data memory - higher 128 byte (80h to FFh)

The address 80h to FFh can be accessed by indirect addressing mode. Address 80h to FFh is data area.

#### 3.5 Data memory - Expanded 1K Bytes (0000h ~ 03FFh)

From external address 0000h to 03FFh is the on-chip expanded SRAM area, total 1K Bytes. This area can be accessed by external direct addressing mode (by instruction MOVX). The address space of instruction MOVX @Ri, i=0, 1 is determined by RCON [7:0] of special function register \$86 RCON (internal RAM control register). The default setting of RCON [7:0] is 00h (page0). One page of data RAM is 256 bytes.

Note: SM39R16A6 can not access (off-chip) external RAM.

| MOVX @Ri, A<br>MOVX A, @Ri | $0 \le RCON[7:0] \le 3$  |

|----------------------------|--------------------------|

|                            | Addr [15:8] <= RCON[7:0] |

# 4. CPU Engine

The SM39R16A6 engine is composed of four components:

- (1) Control unit

- (2) Arithmetic logic unit

- (3) Memory control unit

- (4) RAM and SFR control unit

The SM39R16A6 engine allows to fetch instruction from program memory and to execute using RAM or SFR. The following chapter describes the main engine register.

| Mnemonic | Description                | Dir. | Bit 7    | Bit 6    | Bit 5    | Bit 4            | Bit 3  | Bit 2 | Bit 1        | Bit 0         | RST |

|----------|----------------------------|------|----------|----------|----------|------------------|--------|-------|--------------|---------------|-----|

|          |                            |      |          | 805      | 1 Core   |                  |        |       |              |               |     |

| ACC      | Accumulator                | E0h  | ACC.7    | ACC.6    | ACC.5    | ACC.4            | ACC.3  | ACC.2 | ACC.1        | ACC.0         | H00 |

| В        | B register                 | F0h  | B.7      | B.6      | B.5      | B.4              | B.3    | B.2   | B.1          | B.0           | H00 |

| PSW      | Program status word        | D0h  | CY       | AC       | F0       | RS[              | [1:0]  | OV    | PSW.1        | Р             | 00H |

| SP       | Stack Pointer              | 81h  |          | SP[7:0]  |          |                  |        | 07H   |              |               |     |

| DPL      | Data pointer low 0         | 82h  |          | DPL[7:0] |          |                  |        | H00   |              |               |     |

| DPH      | Data pointer high 0        | 83h  | DPH[7:0] |          |          |                  | H00    |       |              |               |     |

| DPL1     | Data pointer low 1         | 84h  |          |          |          | DPL′             | 1[7:0] |       |              |               | H00 |

| DPH1     | Data pointer high 1        | 85h  |          |          |          | DPH <sup>-</sup> | 1[7:0] |       |              |               | H00 |

| AUX      | Auxiliary register         | 91h  | BRGS     | P21CC    | -        | P1UR             | -      | -     | -            | DPS           | H00 |

| CKCON    | Clock control register     | 8Eh  | -        |          | ITS[2:0] |                  | -      | -     | CLKO         | JT[1:0]       | 10H |

| IFCON    | Interface control register | 8Fh  | -        | CDPR     | -        | -                | -      | -     | -            | ISPE          | 00H |

| PAGESEL  | Page Select                | BEh  | -        | -        | -        | -                | _      | _     | Page_<br>num | Page_<br>mode | 00H |

#### 4.1 Accumulator

ACC is the Accumulator register. Most instructions use the accumulator to store the operand.

| Mnemor | Addre | ess: E0h |       |       |       |       |       |       |  |

|--------|-------|----------|-------|-------|-------|-------|-------|-------|--|

| 7      | 6     | 5        | 4     | 3     | 2     | 1     | 0     | Reset |  |

| ACC.7  | ACC.6 | ACC05    | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 | 00h   |  |

ACC[7:0]: The A (or ACC) register is the standard 8052 accumulator.

## 4.2 B Register

The B register is used during multiply and divide instructions. It can also be used as a scratch pad register to store temporary data.

| Mnemo | nic: B |     |     |     |     |     | Add | ress: F0h |

|-------|--------|-----|-----|-----|-----|-----|-----|-----------|

| 7     | 6      | 5   | 4   | 3   | 2   | 1   | 0   | Reset     |

| B.7   | B.6    | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 | 00h       |

B[7:0]: The B register is the standard 8052 register that serves as a second accumulator.

# 4.3 Program Status Word

| Mnemo | Add | ress: D0h |          |   |    |    |   |       |

|-------|-----|-----------|----------|---|----|----|---|-------|

| 7     | 6   | 5         | 4        | 3 | 2  | 1  | 0 | Reset |

| CY    | AC  | F0        | RS [1:0] |   | OV | F1 | Р | 00h   |

CY: Carry flag.

AC: Auxiliary Carry flag for BCD operations.

F0: General purpose Flag 0 available for user.

RS[1:0]: Register bank select, used to select working register bank.

| RS[1:0] | Bank Selected | Location  |

|---------|---------------|-----------|

| 00      | Bank 0        | 00h – 07h |

| 01      | Bank 1        | 08h – 0Fh |

| 10      | Bank 2        | 10h – 17h |

| 11      | Bank 3        | 18h – 1Fh |

OV: Overflow flag.

F1: General purpose Flag 1 available for user.

P: Parity flag, affected by hardware to indicate odd/even number of "one" bits in the Accumulator, i.e. even parity.

#### 4.4 Stack Pointer

The stack pointer is a 1-byte register initialized to 07h after reset. This register is incremented before PUSH and CALL instructions, causing the stack to start from location 08h.

| Mn | emon     | ic: SP |   |   |   |   |   | Addre | ss: 81h |

|----|----------|--------|---|---|---|---|---|-------|---------|

| 7  | 7        | 6      | 5 | 4 | 3 | 2 | 1 | 0     | Reset   |

|    | SP [7:0] |        |   |   |   |   |   |       | 07h     |

SP[7:0]: The Stack Pointer stores the scratchpad RAM address where the stack begins. In other words, it always points to the top of the stack.

## 4.5 Data Pointer

The data pointer (DPTR) is 2-bytes wide. The lower part is DPL, and the highest is DPH. It can be loaded as a 2-byte register (e.g. MOV DPTR, #data16) or as two separate registers (e.g. MOV DPL,#data8). It is generally used to access the external code or data space (e.g. MOVC A, @A+DPTR or MOVX A,@DPTR respectively).

| Mnemo | nic: DPL  |   |   |   |   |   | Addr | ess: 82h |  |  |  |

|-------|-----------|---|---|---|---|---|------|----------|--|--|--|

| 7     | 6         | 5 | 4 | 3 | 2 | 1 | 0    | Reset    |  |  |  |

|       | DPL [7:0] |   |   |   |   |   |      |          |  |  |  |

DPL[7:0]: Data pointer Low 0

| Mnemoi | nic: DPH  |   |   |   |   |   | Addre | ess: 83h |

|--------|-----------|---|---|---|---|---|-------|----------|

| 7      | 6         | 5 | 4 | 3 | 2 | 1 | 0     | Reset    |

|        | DPH [7:0] |   |   |   |   |   |       | 00h      |

DPH [7:0]: Data pointer High 0

#### 4.6 Data Pointer 1

The Dual Data Pointer accelerates the moves of data block. The standard DPTR is a 16-bit register that is used to address external memory or peripherals. In the SM39R16A6 core the standard data pointer is called DPTR, the second data pointer is called DPTR1. The data pointer select bit chooses the active pointer. The data pointer select bit is located in LSB of AUX register (DPS).

The user switches between pointers by toggling the LSB of AUX register. All DPTR-related instructions use the currently selected DPTR for any activity.

| Mnemonic: DPL1 Address: |            |   |   |   |   |   |   |       |  |  |

|-------------------------|------------|---|---|---|---|---|---|-------|--|--|

| 7                       | 6          | 5 | 4 | 3 | 2 | 1 | 0 | Reset |  |  |

|                         | DPL1 [7:0] |   |   |   |   |   |   |       |  |  |

DPL1[7:0]: Data pointer Low 1

| Mnemo | nic: DPH   | 1 |   |   |   |   | Addre | ss: 85h |  |  |

|-------|------------|---|---|---|---|---|-------|---------|--|--|

| 7     | 6          | 5 | 4 | 3 | 2 | 1 | 0     | Reset   |  |  |

|       | DPH1 [7:0] |   |   |   |   |   |       |         |  |  |

DPH1[7:0]: Data pointer High 1

| Mnemo | Addre | ess: 91h |      |   |   |   |     |       |

|-------|-------|----------|------|---|---|---|-----|-------|

| 7     | 6     | 5        | 4    | 3 | 2 | 1 | 0   | Reset |

| BRGS  | P21CC | -        | P1UR | - | - | - | DPS | 00H   |

DPS: Data Pointer select register.

DPS = 1 is selected DPTR1.

#### 4.7 Clock control register

| Mnemonic: CKCON Address: |   |          |   |   |   |      |         |       |  |  |

|--------------------------|---|----------|---|---|---|------|---------|-------|--|--|

| 7                        | 6 | 5        | 4 | 3 | 2 | 1    | 0       | Reset |  |  |

| -                        |   | ITS[2:0] |   | - | - | CLKO | UT[1:0] | 10H   |  |  |

ITS[2:0]: Instruction timing select.

| ITS [2:0] | Mode              |

|-----------|-------------------|

| 000       | 1T mode           |

| 001       | 2T mode (default) |

| 010       | 3T mode           |

| 011       | 4T mode           |

| 100       | 5T mode           |

| 101       | 6T mode           |

| 110       | 7T mode           |

| 111       | 8T mode           |

CLKOUT[1:0]: Clock output select.

| CLKOUT[1:0] | Mode          |

|-------------|---------------|

| 00          | GPIO(default) |

| 01          | Fosc          |

| 10          | Fosc/2        |

| 11          | Fosc/4        |

It can be used when the system clock is the internal RC oscillator.

# 4.8 Interface control register

Mnemonic: IFCON

Address: 8Fh

7

6

5

4

3

2

1

0

Reset

CDPR

ISPE

00H

CDPR: Code protect (Read Only)

ISPE: ISP function enable bit

ISPE = 1, enable ISP function ISPE = 0, disable ISP function

# 4.9 PAGESEL (Page Select)

The SM39R16A6 provide two different methods to set Special Function Register (SFR) are as follow:

• SFR Method 1 (Indirect Mode): This method is only an SFR page. If you want to use

PWM registers of the Method 2, can be used indirectly addressable setting.

Example: Write a data 0x80h to PWMEN Register in Method 1.

PAGESEL = 0x00; // Method 1.

PWMADDR = 0xF5; // PWMEN indirect address: 0xF5 (Indirect mode)

// (Refer Page1 Table of the Method 2)

PWMDATA = 0x80; // Write data 0x80 to PWMEN.

SFR Method 2 (Page Mode): This method provides two SFR page to set the registers.

Example: Write a data 0x80 to PWMEN Register in Method 2, Page 1.

PAGESEL = 0x03; // Method 2, Page 1 (Page mode)

PWMEN = 0x80; // Write data 0x80 to PWMEN.

• SFR Page Mode Table:

| Page_mode | Page_num | SFR Select           |

|-----------|----------|----------------------|

| 0         | 0        | SFR Method 1         |