# POWER MANAGEMENT CONTROLLER WITH MULTI-CELL SOLAR HARVESTING

#### Description

The EM8502 is an integrated power management solution for low power applications. It is designed to simplify the design of application using multiple solar cells in series that can be directly connected to the application and storage elements.

The device is designed to speed-up system start-up time when the main energy storage element (aka Long Term Storage – LTS) is completely discharged or insufficiently charged to supply the application, by using a secondary energy storage element (Short Term Storage - STS).

When solar energy is high enough the device connects the solar cell to STS or LTS to maintain the supply of the application, while charging the rechargeable element.

The EM8502 is capable of working with a variety of energy elements as secondary storage, namely re-chargeable batteries, supercapacitors or conventional capacitors. In all cases the EM8502 maintains its fast start-up capability that depends only on the harvester conditions and the STS capacitor value.

A USB connection to an external power source is available on the EM8502 for fast charge of the long term storage element.

The EM8502 integrates voltage supervisory functions. Minimum and maximum voltages are controlled on the LTS element to prevent damage to the energy storage element. Harvester minimum voltage monitoring allows disconnecting the solar cell from the storage elements to avoid leakages. Output voltages are kept in a safe range for the application.

To perform granular power management of the application, the EM8502 integrates four independent supply outputs and a sleep mode offering the capability to switch off part or all the supplies.

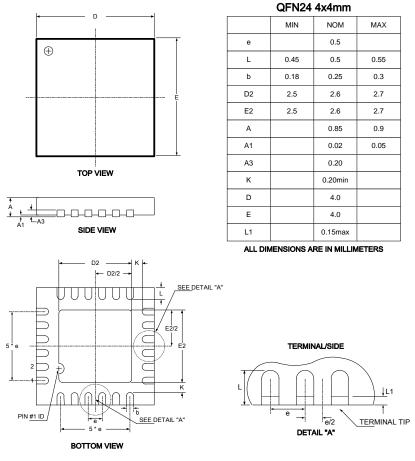

The EM8502 is available in QFN24 package.

#### Features

- Flexible operation with different energy banks

- Secondary cell battery

- Capacitors (gold-cap, super-cap)

- Fast start-up on any energy storage

- Dual energy storage elements

- Start-up on solar cell or on battery

- Power management control

- Multiple independent supply outputs

- Sleep mode and wake-up functions

- User programmable under-voltage and over-voltage levels

- Configurable application voltage

- Battery voltage

- LDO

- Limited external components

- Device configurations are stored in on-chip E<sup>2</sup>PROM

- Dynamic configuration through a SPI or I<sup>2</sup>C interface

- Extended power management status

- Battery on protection mode

- LTS/STS connection status

Minimum/Maximum voltage warning

- USB connected

#### Applications

- Multi-Solar cell platforms

- Wearable systems

- Beacons and wireless sensor networks

- Industrial and environmental monitoring

- Battery operated platforms

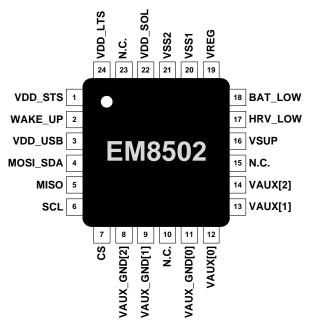

Figure 1 EM8502 QFN24 pins location

# TABLE OF CONTENTS

| 1.                     | Ordering Information                             | . 3 |

|------------------------|--------------------------------------------------|-----|

| 2.                     | Product description                              | . 3 |

| 2.1                    | . Operating modes                                | 3   |

| 2.2                    | . voltage naming conventions                     | 4   |

| 2.3                    | Block diagram                                    | 5   |

| 3.                     | Handling Procedures                              | . 6 |

| 4.                     | Pin description                                  | . 6 |

| 5.                     | Electrical specifications                        |     |

| 5.1                    | . Absolute Maximum Ratings                       | 7   |

| 5.2                    | 5                                                |     |

| 5.3                    | Electrical Characteristics                       | 7   |

| 5.4                    | . Timing diagrams                                | 9   |

| 5                      | .4.1. SPI interface                              | 9   |

| 5                      | .4.2. I2C Interface                              |     |

| 6.                     | Product configuration                            | 10  |

| 6.1                    | . Status information                             | 10  |

| 6.2                    | . Supervising and harvester controller behaviour | 11  |

| 6                      | .2.1. Storage element                            |     |

|                        | .2.2. Harvester power supervisory functions      |     |

| -                      | .2.3. Timing configuration                       |     |

| 6.3                    | 5                                                |     |

| 6.4                    |                                                  |     |

| 6.5                    |                                                  |     |

| 6.6                    |                                                  |     |

| 6.7                    |                                                  | -   |

| -                      | .7.1. Soft reset function                        |     |

|                        | .7.2. Register protection                        |     |

| <b>7.</b>              | Serial interface                                 |     |

| 7.<br>7.1              | •                                                |     |

| 7.1                    |                                                  | -   |

|                        | .2.1. Interface selection                        | -   |

| ,<br>7.3               |                                                  |     |

| -                      | .3.1. Accessing the E2PROM                       |     |

| <b>8.</b> <sup>′</sup> | Register map                                     |     |

| о.<br>9.               | Typical Application                              |     |

|                        |                                                  |     |

|                        | packaging Information                            |     |

| 10.                    |                                                  |     |

| 1                      | 0.1.1. Package marking                           | .28 |

420005-A01, 2.0

## 1. ORDERING INFORMATION

| Part Nb            | Package form | Delivery form | Quantity    |

|--------------------|--------------|---------------|-------------|

| EM8502-A005-LF24B+ | QFN24 4x4 mm | Tape & Reel   | 2500 p/reel |

#### **Table 1 Ordering Information**

For other delivery format please contact EM Microelectronics representative.

## 2. PRODUCT DESCRIPTION

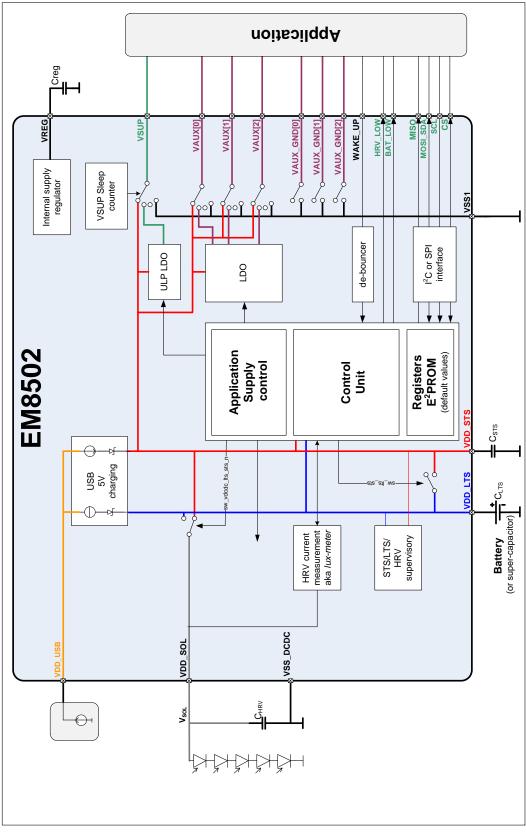

The EM8502 is a power management IC with battery charger function. It manages different energy source elements: a multi-cell solar harvester element through VDD\_SOL, external supply through VDD\_USB, a battery or a Long Term Storage (LTS) through VDD\_LTS. It generates a local supply on a Short Term Storage (STS), visible through VDD\_STS. The EM8502 provides the supply to the application from the energy sources. Surplus energy is stored in a LTS element.

Features and benefits include:

- Power management controller, extending application battery life: the EM8502 supplies the external application through the pins VSUP and VAUX[i]. The voltage is delivered directly from VDD\_STS or through a regulator. On the VSUP pin a wake-up function allows to automatically re-enable the supply after a given time. For external devices using an I<sup>2</sup>C serial interface, it is possible to disconnect their ground through the use of the auxiliary ground pins (VAUX\_GND). This solution avoids supplying the devices connected to a switched-off output supply through the pull-up of I<sup>2</sup>C bus. Overall power consumption is reduced by turning off peripheral ICs through the EM8502.

- Battery charger from solar source: EM8502 manages energy harvesting from a multiple solar cell in series by connecting to LTS and/or STS to maintain the application supply. With its dual storage architecture, application start-up is fast and independent of the battery (LTS) voltage.

- Battery charger from USB source: Fast charging is supported through a USB compatible supply input on the EM8502 (system startup and battery charging to maximum voltage with configurable speed).

- Voltage and current supervisor: The EM8502 includes supervisory functions to detect harvester energy levels detecting (visible through the HRV\_LOW pin) and to monitor low battery voltage levels (visible through the BAT\_LOW pin). The EM8502 protects the battery against over voltage conditions and automatically stops charging when a configurable threshold level is reached.

- Configuration with E<sup>2</sup>PROM, no additional external components: The mode and functional configuration of the EM8502 is controlled by the host MCU through a SPI or an I<sup>2</sup>C interface. Voltage supervision thresholds are set by registers. Configuration parameters are held in on-chip non-volatile memory (E<sup>2</sup>PROM). The EM8502 default configuration parameter values can be modified by the user.

## 2.1. OPERATING MODES

The EM8502 operates in three main modes:

- 1) Normal mode (STS and LTS Connected)

- V<sub>LTS</sub> is inside battery operating range.

- LTS is connected to STS.

- The system can be configured to disconnect VAUX or/and VAUX\_GND pins.

- 2) LTS protection mode (STS and LTS disconnected)

- EM8502 enters this mode when V<sub>LTS</sub> drops below minimum battery operation (v\_bat\_min\_lo).

- BAT\_LOW pin is set to '1'.

- LTS and STS are disconnected to protect LTS against under voltage condition.

- VSUP and VAUX are maintained by the multiple solar cells connected on VDD\_SOL or by VDD\_USB through a LDO.

- 3) Sleep mode

- VSUP is not supplied no communication on SPI/I<sup>2</sup>C interface.

- VSUP can be re-activated by WAKE\_UP pin or internal timer.

## 2.2. VOLTAGE NAMING CONVENTIONS

To describe the operation of this product, the following set of voltage naming conventions is adopted throughout this document, Table 2:

| NAME               | DESCRIPTION                                                                                                                                                                                                                                                                                                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v_bat_max_hi       | Maximum battery voltage. High level of hysteresis.                                                                                                                                                                                                                                                          |

| v_bat_min_hi_dis   | Minimum STS maintenance voltage – acts as v_bat_min_hi when STS and LTS are disconnected                                                                                                                                                                                                                    |

| v_bat_min_hi_con   | Minimum battery maintenance voltage – acts as v_bat_min_hi when STS and LTS are connected                                                                                                                                                                                                                   |

| v_bat_min_hi       | Minimum battery voltage. High level of hysteresis<br>Equal to <b>v_bat_min_hi_dis</b> or <b>v_bat_min_hi_con</b> according to the connection state in between STS and LTS.<br>The term " <b>v_bat_min_hi</b> " is used here whenever there is no specific usage of the connected and disconnected<br>values |

| v_bat_min_lo       | Minimum battery voltage. Low level of hysteresis                                                                                                                                                                                                                                                            |

| v_apl_max_hi       | Maximum application voltage. High level of hysteresis                                                                                                                                                                                                                                                       |

| v_apl_max_lo       | Maximum application voltage. Low level of hysteresis                                                                                                                                                                                                                                                        |

| V <sub>cs_hi</sub> | Cold start voltage level                                                                                                                                                                                                                                                                                    |

| v_ulp_ldo          | Regulated voltage on VSUP pin                                                                                                                                                                                                                                                                               |

Table 2 Voltage Naming Conventions

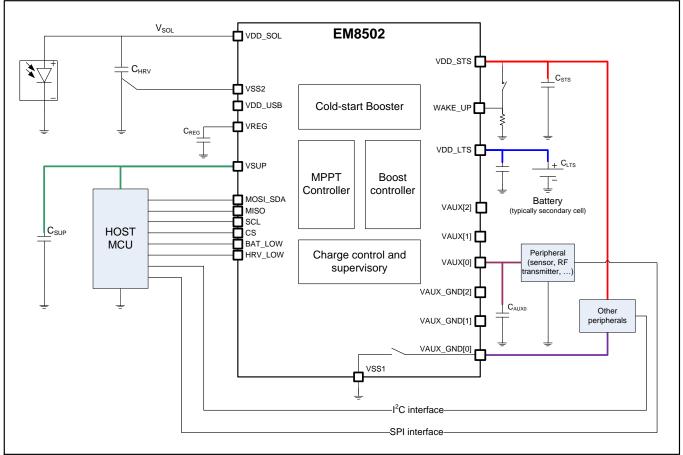

## 2.3. BLOCK DIAGRAM

Figure 2-1 EM8502 Block Diagram

# 3. HANDLING PROCEDURES

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level.

## 4. **PIN DESCRIPTION**

|     | PIN         | I/O T     | YPE        | DESCRIPTION                                                |

|-----|-------------|-----------|------------|------------------------------------------------------------|

| NO. | NAME        | DIRECTION | SUPPLY     |                                                            |

| 1   | VDD_STS     | I/O       | -          | Connection for the Short Term energy Storage element (STS) |

| 2   | WAKE_UP     | Input     | up to 3.6V | Wake-up pin                                                |

| 3   | VDD_USB     | Input     | -          | USB power supply connection                                |

| 4   | MOSI_SDA    | Input     | VSUP       | SPI MOSI or I2C SDA connection                             |

| 5   | MISO        | Output    | VSUP       | SPI MISO connection                                        |

| 6   | SCL         | Input     | VSUP       | SPI or I2C clock                                           |

| 7   | CS          | Input     | VSUP       | SPI chip select and SPI/I2C selection mode(when at '1')    |

| 8   | VAUX_GND[2] | Output    | -          | Auxiliary 2 ground connection                              |

| 9   | VAUX_GND[1] | Output    | -          | Auxiliary 1 ground connection                              |

| 10  | N.C.        |           |            |                                                            |

| 11  | VAUX_GND[0] | Output    | -          | Auxiliary 0 ground connection                              |

| 12  | VAUX[0]     | Output    | -          | Auxiliary 0 supply output connection                       |

| 13  | VAUX[1]     | Output    | -          | Auxiliary 1 supply output connection                       |

| 14  | VAUX[2]     | Output    | -          | Auxiliary 2 supply output connection                       |

| 15  | N.C.        |           |            |                                                            |

| 16  | VSUP        | Output    | -          | Main supply output                                         |

| 17  | HRV_LOW     | Output    | VSUP       | Energy harvester cell low indicator (when at '1')          |

| 18  | BAT_LOW     | Output    | VSUP       | Battery low indicator (when at '1')                        |

| 19  | VREG        | Output    | -          | Regulated voltage connection                               |

| 20  | VSS1        | Supply    | -          | Device ground connection                                   |

| 21  | VSS2        | Supply    | -          | Device ground connection                                   |

| 22  | VDD_SOL     | Input     | -          | Direct connection from the solar cell                      |

| 23  | N.C.        |           |            |                                                            |

| 24  | VDD_LTS     | I/O       | -          | Connection for the Long Term energy Storage element (LTS)  |

#### Table 3 Pin-out description

The digital pads are all supplied by VSUP, with the exception of the WAKE\_UP pad whose trigger levels are independent of the supply voltages. When VSUP is disabled these pads are floating therefore the communication interface is off. All digital pads are active HIGH.

# 5. ELECTRICAL SPECIFICATIONS

## 5.1. ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                                      | VA      | LUE                   | UNIT |

|----------------------------------------------------------------|---------|-----------------------|------|

| PARAMETER                                                      | MIN     | MAX                   |      |

| Power supply VDD_STS, VDD_LTS, VDD_SOL                         | -0.2    | 4.2                   | V    |

| Power supply VDD_USB                                           | -0.2    | 8.0                   | V    |

| Input voltage                                                  | VSS-0.2 | V <sub>SUP</sub> +0.2 | V    |

| Input voltage (pin WAKE_UP)                                    | -0.2    | 3.8                   | V    |

| Storage Temperature Range (T <sub>STG</sub> )                  | -65     | 150                   | O°   |

| Electrostatic discharge to ANSI/ESDA/JEDEC JS-001-2014 for HBM | -2000   | 2000                  | V    |

#### Table 4 Absolute maximum ratings

Stresses at or above these listed under Absolute Maximum Ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

Warning: The device is not functional when exposed to light. When a non-packaged version is used, it is mandatory to protect the device from light (e.g. glob-top, non-transparent package, metal shield on the PCB ...)

## 5.2. OPERATING CONDITIONS

| PARAMETER                              | SYMBOL           | MIN   | TYP | MAX                  | UNIT |

|----------------------------------------|------------------|-------|-----|----------------------|------|

| Solar input                            | V <sub>SOL</sub> |       |     | 3.8                  | V    |

| Long Term energy Storage bank voltage  | VLTS             |       | 3.0 | 3.6                  | V    |

| Short Term energy Storage bank voltage | V <sub>STS</sub> |       | 3.0 | 3.6                  | V    |

| VDD_USB voltage                        | VUSB             |       | 5   | 5.5                  | V    |

| Long term capacitor <sup>(1)</sup>     | CLTS             | 0.001 |     |                      | F    |

| Short term capacitor <sup>(2)</sup>    | CSTS             | 47    |     |                      | μF   |

| Regulated voltage capacitor            | CREG             | 470   |     |                      | nF   |

| Harvester capacitor (nominal value)    | CHRV             |       | 1   |                      | μF   |

| VSUP capacitor                         | C <sub>SUP</sub> | 1     |     | 0.1*C <sub>STS</sub> | μF   |

| VAUX capacitor                         | CAUX             | 1     |     | 0.1*Csts             | μF   |

| Input inductance                       | L <sub>1</sub>   | 37.6  | 47  | 56.4                 | μH   |

(1) When using a super-capacitor

(2) CSTS shall be greater than 10 times CHRV to avoid drops on STS when switching back and forth in between connection to LTS and STS

#### **Table 5 Operating Conditions**

## 5.3. ELECTRICAL CHARACTERISTICS

Unless otherwise specified: T<sub>A</sub>=-40 to +85°C for min max specifications and T<sub>A</sub>= 25°C for typical specifications.

| PARAMETER                                        | SYMBOL                  | CONDITIONS                                                                  | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------------------|-------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| CURRENT CONSUMPTIONS ON LTS                      | ÷                       | <u>.</u>                                                                    |      |      |      |      |

| IDD in "LTS protection mode" and "HRV low        | ILTS_prot1              | Battery supervisory at 4Hz; VSUP and VAUX LDOs disabled                     |      | 65   |      | nA   |

| mode"                                            | p                       |                                                                             |      |      |      |      |

| IDD in "LTS protection mode"                     | ILTS prot2              | Battery supervisory at 4Hz; VSUP and VAUX LDOs disabled                     |      | 15   |      | nA   |

| IDD in "HRV low mode" STS and LTS connected      | HRV_lo2                 | Battery supervisory at 4Hz; VSUP and VAUX LDOs disabled                     |      | 145  |      | nA   |

| IDD in "HRV low mode" STS and LTS connected      | I <sub>HRV_lo3</sub>    | Battery supervisory at 4Hz; ULP LDO enabled and VAUX LDO<br>disabled        |      | 170  |      | nA   |

| IDD in "HRV low mode" STS and LTS connected      | I <sub>HRV_lo4</sub>    | Battery supervisory at 4Hz; VSUP and VAUX[0] LDO enabled                    |      | 285  |      | nA   |

| IDD in "HRV low mode" STS and LTS connected      | HRV 105                 | Battery supervisory at 4Hz; VSUP and VAUX[1] LDO enabled                    |      | 265  |      | nA   |

| IDD in "HRV low mode" STS and LTS connected      | HRV lo6                 | Battery supervisory at 4Hz; VSUP and VAUX[2] LDO enabled                    |      | 250  |      | nA   |

| IDD in "HRV low mode" STS and LTS connected      | HRV_lo6                 | Battery supervisory at 4Hz; VSUP and all VAUX LDO enabled                   |      | 380  |      | nA   |

| IDD in "normal mode" STS and LTS<br>disconnected | INORM                   | Battery supervisory at 4Hz; VSUP and VAUX LDOs disabled (VDD STS < VDD LTS) |      | 45   |      | nA   |

| QUIESCENT CURRENT AND LEAKAGE C                  | N STS (WHEN             | LTS IS NOT CONNECTED TO STS)                                                |      |      |      |      |

| IDD in "HRV low mode"                            | I <sub>STS_hrvlo</sub>  | Battery supervisory at 4Hz; VSUP and VAUX LDOs disabled                     |      | 65   |      | nA   |

| VSUP AND VAUX LDO VOLTAGE LEVEL                  | 010_1110                |                                                                             |      |      |      |      |

| ULP/VAUX LDO level 0                             |                         | VSTS - VSUP> 0.3V                                                           | 1.08 | 1.2  | 1.32 | V    |

| ULP/VAUX LDO level 1                             |                         | Vsts - Vsup> 0.3V                                                           | 1.39 | 1.55 | 1.71 | V    |

| ULP/VAUX LDO level 2                             |                         | Vsts - Vsup> 0.3V                                                           | 1.48 | 1.65 | 1.82 | V    |

| ULP/VAUX LDO level 3                             |                         | $V_{STS} - V_{SUP} > 0.3V$                                                  | 1.62 | 1.8  | 1.98 | V    |

| ULP/VAUX LDO level 4                             |                         | V <sub>STS</sub> – V <sub>SUP</sub> > 0.3V                                  | 1.8  | 2    | 2.2  | V    |

| ULP/VAUX LDO level 5                             |                         | V <sub>STS</sub> – V <sub>SUP</sub> > 0.3V                                  | 1.98 | 2.2  | 2.42 | V    |

| ULP/VAUX LDO level 6                             |                         | V <sub>STS</sub> – V <sub>SUP</sub> > 0.3V                                  | 2.16 | 2.4  | 2.64 | V    |

| ULP/VAUX LDO level 7                             |                         | V <sub>STS</sub> – V <sub>SUP</sub> > 0.3V                                  | 2.34 | 2.6  | 2.86 | V    |

| MAXIMUM CURRENT ON THE ULP AND                   | AUX LDO                 |                                                                             |      |      |      |      |

| Maximum current on ULP LDO                       |                         | Drop from open voltage is 100 mV, LDO level at 1.8V                         |      | 10   |      | mA   |

| Maximum current on VAUX[0] LDO                   |                         | Drop from open voltage is 100 mV, LDO level at 1.8V                         |      | 20   |      | mA   |

| Maximum current on VAUX[1] LDO                   |                         | Drop from open voltage is 100 mV, LDO level at 1.8V                         |      | 10   |      | mA   |

| Maximum current on VAUX[2] LDO                   |                         | Drop from open voltage is 100 mV, LDO level at 1.8V                         |      | 5    |      | mA   |

| SWITCH RESISTOR                                  |                         |                                                                             |      |      |      |      |

| VDD_LTS to VDD_STS                               | R <sub>sw_lts_sts</sub> | VDD_STS at 3V                                                               |      | 3.1  |      | Ω    |

| VDD_STS to VSUP                                  | R <sub>sw_VSUP</sub>    | VDD_STS at 3V                                                               |      | 7.4  |      | Ω    |

| VDD_STS to VAUX[0]                               | Rsw_VAUX0               | VDD_STS at 3V                                                               |      | 4.4  |      | Ω    |

| VDD_STS to VAUX[1]                               | R <sub>sw_VAUX1</sub>   | VDD_STS at 3V                                                               |      | 5.8  |      | Ω    |

| VDD_STS to VAUX[2]                               | Rsw_VAUX2               | VDD_STS at 3V                                                               |      | 6.4  |      | Ω    |

| VAUX_GND[0] to VSS                               | R <sub>sw_GND0</sub>    | VDD_STS at 3V                                                               |      | 4.74 |      | Ω    |

| VAUX_GND[1,2] to VSS                             | Rsw_GND1,2              | VDD_STS at 3V                                                               |      | 5.62 |      | Ω    |

| SUPERVISORY LEVELS ON STS, LTS AN                | ID HRV <sup>(1)</sup>   |                                                                             |      |      |      |      |

| Maximum voltage                                  |                         |                                                                             |      |      | 3.6  | V    |

| Level step from IvI0 to IvI15                    | VIvI_15                 |                                                                             |      | 73   |      | mV   |

| Level step from lvl16 to lvl30 (1.24V to 2.26V)  | V <sub>Ivl_30</sub>     |                                                                             | 67.9 | 73   | 78.1 | mV   |

# EM8502

| PARAMETER                                      | SYMBOL                  | CONDITIONS                                            | MIN  | TYP              | MAX  | UNIT |

|------------------------------------------------|-------------------------|-------------------------------------------------------|------|------------------|------|------|

| Level step from IvI31 to IvI54 (2.34V to 4.2V) | VIvI_54                 |                                                       | 69.4 | 73               | 76.7 | mV   |

| Differential non linearity                     |                         |                                                       |      | ±0.5             |      | LSB  |

| Number of levels                               |                         |                                                       |      | 50               |      |      |

| HARVESTER CURRENT LEVEL DETECT                 |                         | ER                                                    |      |                  |      |      |

| Harvester current level step                   | Ihrv_check_lvl          |                                                       |      | 1                |      | μΑ   |

| Luxmeter current detection level               | I <sub>lux_Ivi</sub>    |                                                       |      | 2 <sup>1vl</sup> |      | μΑ   |

| "Ivl" = level used for the measurement [015]   |                         |                                                       |      |                  |      |      |

| Short circuit voltage                          | V <sub>hrv_scv</sub>    |                                                       |      | 70               |      | mV   |

| USB POWER                                      |                         |                                                       |      |                  |      |      |

| Minimum voltage for USB charging detection     | V <sub>usb_min</sub>    |                                                       |      | 3.5              |      | V    |

| Regulated voltage on VDD_STS                   | VUSB_REG                |                                                       |      | 2.1              |      | V    |

| Current source level 0 on LTS                  | I <sub>USB_IVI0</sub>   |                                                       |      | 0                |      | mA   |

| Current source level 1 on LTS                  | USB_IVI1                |                                                       |      | 6.9              |      | mA   |

| Current source level 2 on LTS                  | USB_IVI2                |                                                       |      | 12.7             |      | mA   |

| Current source level 3 on LTS                  | IUSB_IVI3               |                                                       |      | 20.6             |      | mA   |

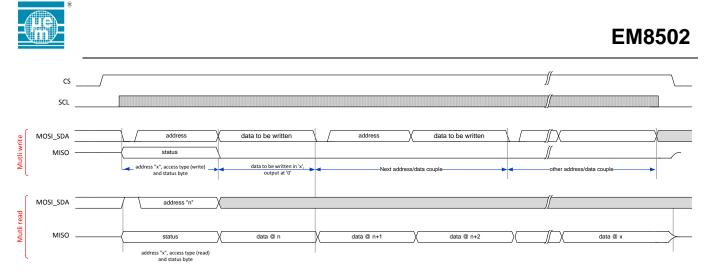

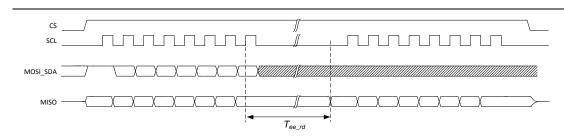

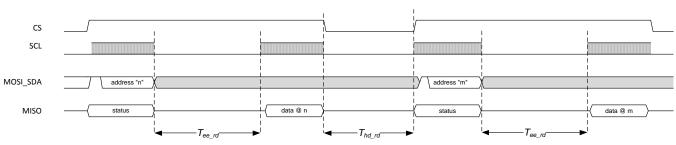

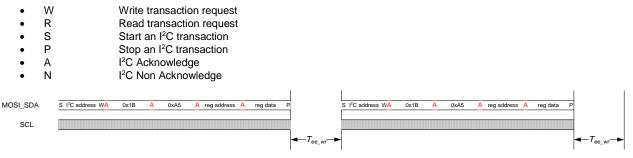

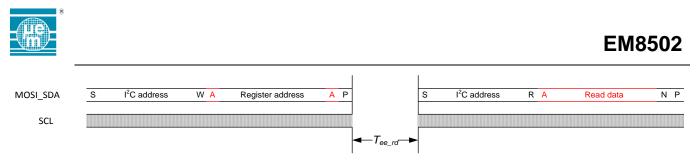

| E2PROM PARAMETERS                              |                         |                                                       |      |                  |      |      |

| E <sup>2</sup> PROM write time                 | T <sub>ee_wr</sub>      |                                                       |      |                  | 8    | ms   |

| E <sup>2</sup> PROM read time                  | T <sub>ee_rd</sub>      |                                                       |      |                  | 0.9  | ms   |

| E2PROM maximum write cycle                     | N <sub>ee_cyc</sub>     |                                                       | 1000 |                  |      |      |

| E2PROM read hold time                          | T <sub>hd_rd</sub>      |                                                       |      |                  | 10   | μs   |

| INTERFACE PARAMETERS                           |                         |                                                       |      |                  |      |      |

| Input WAKE_UP - low level                      | V <sub>il_wk</sub>      | V <sub>LTS</sub> =1.2V to 3.6V                        |      |                  | 0.3  | V    |

| Input WAKE_UP - high level                     | V <sub>ih_wk</sub>      | V <sub>LTS</sub> =1.2V to 3.6V                        | 0.9  |                  |      | V    |

| Wake-up rising edge reaction time              | T <sub>r_wk</sub>       | Debouncer disabled                                    |      | 4.5              |      | μs   |

| Wake-up falling edge reaction time             | Tf_wk                   | Debouncer disabled                                    |      | 120              |      | μs   |

| Input - low level                              | V <sub>il_si</sub>      | V <sub>SUP</sub> =1.2V to 3.6V                        |      |                  | 0.2* | V    |

|                                                |                         |                                                       |      |                  | VSUP |      |

| Input - high level                             | V <sub>ih_si</sub>      | V <sub>SUP</sub> =1.2V to 3.6V                        | 0.8* |                  |      | V    |

|                                                |                         |                                                       | VSUP |                  |      |      |

| Output – low level for I2C                     | l <sub>ol_sda</sub>     | V <sub>SUP</sub> =1.8V, Vol=0.2* V <sub>SUP</sub>     | 3    |                  |      | mA   |

| Output – low level for I2C                     | ol_sda_1.2              | V <sub>SUP</sub> =1.20V, Vol=0.23*Vsup                | 3    |                  |      | mA   |

| Output – low level                             | loi                     | V <sub>SUP</sub> =1.8V, Vol=0.2*Vsup                  | 1    |                  |      | mA   |

|                                                |                         | (MISO, MOSI_SDA, BAT_LOW, HRV_LOW)                    |      |                  |      |      |

| Output – low level                             | I <sub>ol_1.2</sub>     | V <sub>SUP</sub> =1.20V, Vol=0.23*Vsup                | 1    |                  |      | mA   |

| Output high land                               |                         | (MISO, MOSI_SDA, BAT_LOW, HRV_LOW)                    |      |                  |      |      |

| Output – high level                            | I <sub>oh</sub>         | $V_{SUP} = 1.8V$ , Voh=0.8*Vsup                       |      |                  | -1   | mA   |

|                                                |                         | (MISO, MOSI_SDA, BAT_LOW, HRV_LOW)                    |      |                  | 1    |      |

| Output – high level                            | I <sub>oh_1.2</sub>     | V <sub>SUP</sub> =1.2V, Voh=0.8*Vsup                  |      |                  | -1   | mA   |

| I <sup>2</sup> C bus load capacitor            | Cb                      | (MISO, MOSI_SDA, BAT_LOW, HRV_LOW)                    |      |                  | 400  | ~F   |

|                                                | Ub                      | On MOSI_SDA and SCL                                   |      |                  | 400  | pF   |

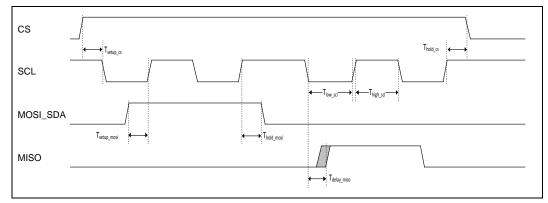

| SPITIMINGS                                     |                         | 1                                                     |      |                  | _    |      |

| SPI clock input frequency                      | F <sub>spi</sub>        |                                                       |      |                  | 5    | MHz  |

| SCL low pulse                                  | T <sub>low_scl</sub>    |                                                       | 20   |                  |      | ns   |

| SCL high pulse                                 | T <sub>high_scl</sub>   |                                                       | 20   |                  | 1    | ns   |

| MOSI_SDA setup time                            | T <sub>setup</sub> mosi |                                                       | 20   |                  |      | ns   |

| MOSI SDA hold time                             | Thold mosi              |                                                       | 20   |                  |      | ns   |

| MISO output delay                              | T <sub>delay_miso</sub> | 25pF load, V <sub>SUP</sub> =1.6V min                 | 20   |                  | 30   | ns   |

| MISO output delay                              |                         | $25\text{pF}$ load, $V_{\text{SUP}} = 1.0V$ min       |      |                  | 40   | -    |

|                                                | T <sub>delay_miso</sub> | $25\mu$ idau, $v_{SUP} = 1.2v$ min                    | 50   |                  | 40   | ns   |

| CS setup time                                  | T <sub>setup_cs</sub>   |                                                       | 50   |                  |      | ns   |

| CS hold time                                   | Thold_cs                |                                                       | 20   |                  |      | ns   |

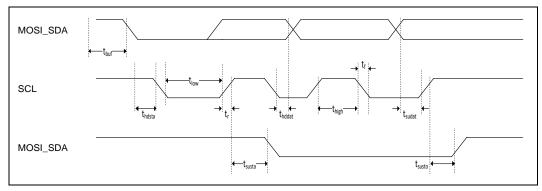

| I <sup>2</sup> C TIMINGS <sup>(2)</sup>        |                         |                                                       |      |                  |      |      |

| MOSI_SDA setup time                            | t <sub>sudat</sub>      | Standard & Fast Modes                                 | 160  |                  |      | ns   |

|                                                | Juda                    | High Speed Mode                                       | 30   |                  |      | ns   |

| MOSI SDA hold time                             | t <sub>hddat</sub>      | Standard & Fast Modes with C <sub>b</sub> =100pF Max. | 80   |                  |      | ns   |

|                                                | inddat                  |                                                       | 90   |                  |      | -    |

|                                                |                         | Standard & Fast Modes with $C_b = 400 pF$ Max         |      |                  | 445  | ns   |

|                                                |                         | High Speed Mode with C <sub>b</sub> =100pF Max.       | 18   |                  | 115  | ns   |

|                                                |                         | High Speed Mode with Cb=400pF Max.                    | 24   |                  | 150  | ns   |

| SCL low pulse                                  | t <sub>low</sub>        | High Speed Mode with Cb=100pF Max.                    | 160  |                  | 1    | ns   |

|                                                |                         | V <sub>SUP</sub> =1.62V                               |      |                  | 1    |      |

| SCL low pulse                                  | t <sub>low</sub>        | High Speed Mode with $C_b=100$ pF Max. $V_{SUP}=1.2V$ | 210  |                  |      | ns   |

| DOF IOM PUIDE                                  | LIOW                    | 1  mgh  opccd mode with Ob- roopt max. VSUP = 1.2 V   | 210  |                  |      | 113  |

The v\_bat\_max, v\_apl\_min with their hysteresis can be set according to the supervising levels. E.g. for v\_bat\_max, both v\_bat\_max\_lo and v\_bat\_max\_hi will have to be set accordingly.

Refers to I<sup>2</sup>C specification 2.1 (January 2000)

## **Table 6 Electrical Specifications**

## 5.4. TIMING DIAGRAMS

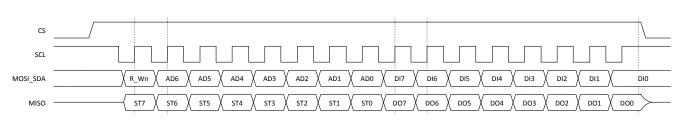

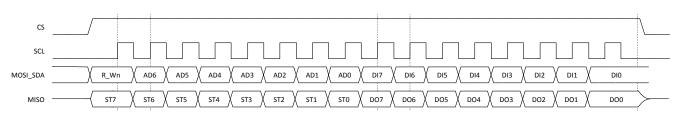

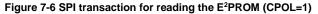

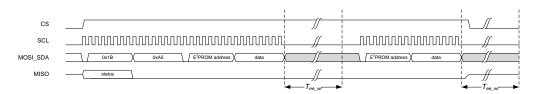

### 5.4.1. SPI INTERFACE

### Figure 5-1 4-wire SPI Timing Diagram

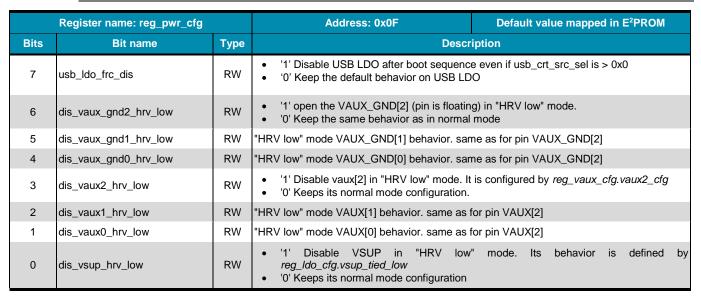

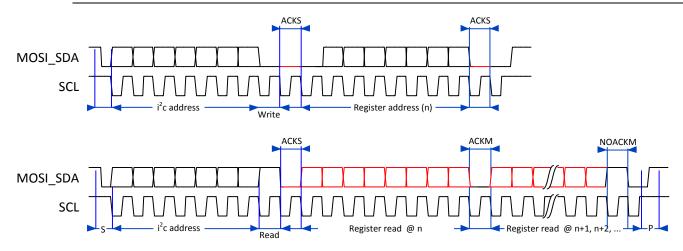

## 5.4.2. I2C INTERFACE

# 6. PRODUCT CONFIGURATION

The EM8502 is an autonomous power management system able to manage power domains, power sources and storage elements.

At start-up the device enters a boot sequence. It controls the state of both energy storage elements, and sets the default configuration parameters of the device by retrieving the corresponding values from the on-chip E<sup>2</sup>PROM.

Upon completion of the boot sequence the system enters the supervising and harvester controller state ("normal mode"). It is now possible to modify configuration parameters through the serial interface to change the behavior of the device. When updating the device configuration through the serial interface it is recommended to write the complete set of EM8502 configuration parameters in a single transaction (see §7).

EM8502 is able to operate autonomously by using default configuration values from the on-chip E<sup>2</sup>PROM.

## 6.1. STATUS INFORMATION

EM8502 provides status feed-back as follows.

- To allow fast system response the pins HRV\_LOW and BAT\_LOW directly indicate the status of the harvester cell and the battery to the host MCU.

- Additional status information is provided through register *reg\_status*. During an SPI transaction the *reg\_status* value sent as the first byte (along with the indication from the MCU of the address to be accessed). In case of an I2C transaction the *reg\_status* register has to be polled explicitly.

|      | Register Name: reg_statu | s    |       | Address: 0x22                                                                                                                                                                                                                            |  |  |  |  |

|------|--------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bits | Bit name                 | Туре | Reset | Description                                                                                                                                                                                                                              |  |  |  |  |

| 7    | eeprom_data_busy         | RO   | 0     | <ul> <li>'1' EEPROM being written. Wait for new configuration</li> <li>'0' EEPROM ready to be written. New configuration can be written</li> </ul>                                                                                       |  |  |  |  |

| 6    | hrv_lux_busy             | RO   | 0     | <ul> <li>'1' lux-meter or HRV current supervisory is running</li> <li>'0' no current measurement on the harvester on-going.</li> </ul>                                                                                                   |  |  |  |  |

| 5    | hrv_low                  | RO   | 0     | <ul> <li>'1' HRV energy level too low for harvesting</li> <li>'0' HRV has enough energy to be harvested</li> </ul>                                                                                                                       |  |  |  |  |

| 4    | bat_low                  | RO   | 0     | <ul> <li>'1' LTS voltage lower than v_bat_min_hi in normal mode, lower than v_bat_min_lo in primary cell mode</li> <li>'0' LTS voltage higher than v_bat_min_hi in normal mode, higher than v_bat_min_lo in primary cell mode</li> </ul> |  |  |  |  |

| 3    | sw_solar_lts_nsts        | RO   | 0     | <ul> <li>'1' Solar cell connected to LTS</li> <li>'0' Solar cell connected to STS</li> </ul>                                                                                                                                             |  |  |  |  |

| 2    | sw_lts_sts               | RO   | 0     | <ul> <li>'1' LTS and STS are connected</li> <li>'0' STS is disconnected from LTS</li> </ul>                                                                                                                                              |  |  |  |  |

| 1    | usb_on                   | RO   | 0     | <ul> <li>'1' USB power has been detected</li> <li>'0' No USB power found</li> </ul>                                                                                                                                                      |  |  |  |  |

| 0    | lts_protect              | RO   | 0     | <ul> <li>'1' LTS protection mode activated (V<sub>LTS</sub> &lt; v_bat_min_lo)</li> <li>'0' LTS protection mode inactive (V<sub>LTS</sub> &gt; v_bat_min_lo)</li> </ul>                                                                  |  |  |  |  |

#### Table 7 Status Register (0x22)

EM8502 offers great flexibility in being configured for different system applications and use cases. The following chapters provide detailed descriptions of all configuration parameters and registers available to the user.

## 6.2. SUPERVISING AND HARVESTER CONTROLLER BEHAVIOUR

### 6.2.1. STORAGE ELEMENT

Storage element voltage and state are available through the *reg\_vld\_status* register.

|      | Reguster name: reg_vld_sta | itus |       | Address: 0x23                                                                                             |

|------|----------------------------|------|-------|-----------------------------------------------------------------------------------------------------------|

| Bits | Bit name                   | Туре | Reset | Description                                                                                               |

| 7    | lts_bat_min_hi             | RO   | 0     | <ul> <li>'1' V<sub>LTS</sub> &gt; v_bat_min_hi</li> <li>'0' V<sub>LTS</sub> &lt;= v_bat_min_hi</li> </ul> |

| 6    | lts_bat_min_lo             | RO   | 0     | <ul> <li>'1' V<sub>LTS</sub> &gt; v_bat_min_lo</li> <li>'0' V<sub>LTS</sub> &lt;= v_bat_min_lo</li> </ul> |

| 5    | sts_bat_max_hi             | RO   | 0     | <ul> <li>'1' V<sub>STS</sub> &gt; v_bat_max_hi</li> <li>'0' V<sub>STS</sub> &lt;= v_bat_max_hi</li> </ul> |

| 4    | sts_bat_max_lo             | RO   | 0     | <ul> <li>'1' V<sub>STS</sub> &gt; v_bat_max_lo</li> <li>'0' V<sub>STS</sub> &lt;= v_bat_max_lo</li> </ul> |

| 3    | sts_apl_max_hi             | RO   | 0     | <ul> <li>'1' V<sub>STS</sub> &gt; v_apl_max_hi</li> <li>'0' V<sub>STS</sub> &lt;= v_apl_max_hi</li> </ul> |

| 2    | sts_apl_max_lo             | RO   | 0     | <ul> <li>'1' V<sub>STS</sub> &gt; v_apl_max_lo</li> <li>'0' V<sub>STS</sub> &lt;= v_apl_max_lo</li> </ul> |

| 1    | sts_bat_min_hi             | RO   | 0     | <ul> <li>'1' V<sub>STS</sub> &gt; v_bat_min_hi</li> <li>'0' V<sub>STS</sub> &lt;= v_bat_min_hi</li> </ul> |

| 0    | sts_bat_min_lo             | RO   | 0     | <ul> <li>'1' V<sub>STS</sub> &gt; v_bat_min_lo</li> <li>'0' V<sub>STS</sub> &lt;= v_bat_min_lo</li> </ul> |

#### Table 8 Voltage Status Register (0x23)

Operation of the two energy banks (LTS and STS) is performed through three key voltage threshold levels.

• Minimum battery level voltage

Maximum battery level voltage

Maximum application level voltage

- v\_bat\_min (reg\_v\_bat\_min\_hi\_con or reg\_v\_bat\_min\_hi\_dis and reg\_v\_bat\_min\_lo)

- v\_bat\_max (reg\_v\_bat\_max\_hi and reg\_v\_bat\_max\_lo)

v\_apl\_max (reg\_v\_apl\_max\_hi and reg\_v\_apl\_max\_lo)

The three levels include a hysteresis to avoid instability of the controller. The hysteresis values have to be carefully chosen according to the application and have to fulfill the following conditions:

- v\_bat\_min\_hi\_dis > v\_bat\_min\_hi\_con > v\_bat\_min\_lo

- v\_apl\_max\_hi > v\_apl\_max\_lo

- v\_bat\_max\_hi > v\_bat\_max\_lo

If  $v_apl_max \ge v_bat_max$  the application maximum level is considered to be the maximum battery level.

Supervising of the minimum battery level is performed through two registers for its highest control level (v\_bat\_min\_hi). When the two battery banks are not connected v\_bat\_min\_hi\_dis is used to inform the system when it has to charge STS again (see phase 4 to 5 in Error! Reference ource not found. on page Error! Bookmark not defined.). When LTS and STS are connected together v\_bat\_min\_hi\_con is used as supervising level.

The minimum value allowed for the **v\_bat\_min\_hi\_dis** register is 0x15 corresponding to typically 1.47 V. For any value lower than this minimum the system may shut-down without notification through the BAT\_LOW pin.

#### All voltage levels with prefix " $v_{-}$ " are configured by register according to the following equation:

#### v\_<voltage name> = V<sub>IvI</sub> \* (reg\_<voltage name>+1)

Supervisory status of the battery is also visible through the pin BAT\_LOW. When the  $V_{LTS}$  is below **v\_bat\_min\_hi** for two consecutive measurements, BAT\_LOW is asserted (set to VSUP level). When two measurements show that  $V_{LTS}$  is above **v\_bat\_min\_hi**, BAT\_LOW is de-asserted (set to VSS). The only exception is during the boot phase where the BAT\_LOW signal is asserted after the first measurement of  $V_{LTS}$ .

The EM8502 protects the battery when its voltage is too low. This corresponding threshold level can be set through the  $v_bat_min_lo$  register. When  $V_{LTS}$  is falling below this value the EM8502 operates only on the harvester.

#### 6.2.2. HARVESTER POWER SUPERVISORY FUNCTIONS

The EM8502 monitors harvester power to prevent reverse current from the energy storage (LTS). The detection is done regularly through a current sensor. The device is sensing the current at the voltage  $V_{hrv\_sov}$  delivered by the solar cell. The current threshold of detection is set through the *reg\_hrv\_check\_lvl.hrv\_check\_lvl* register to disconnect the solar cell from the energy banks. To return to the running state, the EM8502 detection is done with a different principle. The current measurement is done by connecting a resistance on VDD\_SOL and sense voltage on this pin using **v\_hrv\_min** voltage level.

#### Resistances and currents are defined in reg\_hrv\_check\_lvl.hrv\_check\_lvl:

| reg_hrv_check_lvl.hrv_check_lvl | 0x00 | 0x01 | 0x02 | 0x03 | 0x04 | 0x05 | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

|---------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Current (µA)                    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   |

| Resistance (kΩ)                 | 35   | 23.3 | 17.5 | 14   | 11.7 | 10   | 8.75 | 7.8  | 7    | 6.36 | 5.38 | 5.4  | 5    | 4.7  | 4.4  | 4.4  |

#### **Table 9 HRV Current Detection Levels**

Configuration example:

• reg\_hrv\_check\_lvl =0x00; reg\_v\_hrv\_cfg = 0x00

The system indicates HRV\_LOW ='1' from 1µA at  $V_{hrv\_scv}$  (70mV) and remains off until  $V_{IvI}$  is reached with 35 k $\Omega$  load on VDD\_SOL (2 µA at  $V_{IvI}$ ). A hysteresis of 1 µA is applied.

|      | Register name: reg_v_hrv_cfg |      | Address: 0x04                                                                                                                                                                                                                                             | Default value mapped in E <sup>2</sup> PROM |  |  |  |  |

|------|------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|

| Bits | Bit name                     | Туре | Description                                                                                                                                                                                                                                               |                                             |  |  |  |  |

| 7    | -                            | -    | Reserved                                                                                                                                                                                                                                                  |                                             |  |  |  |  |

| 6    | -                            | RW   | To be written always to '0'                                                                                                                                                                                                                               |                                             |  |  |  |  |

| 5:0  | v_hrv_min                    | RW   | Minimum HRV open voltage required to generate energy.<br>V <sub>hrv_min</sub> = V <sub>Ivl</sub> * (reg_v_hrv_min(5:0)+1)<br>if V <sub>HRV</sub> < V <sub>hrv_min</sub> and <i>reg_v_hrv_cfg.hrv_check_vld</i> = '1' then <i>reg_status.hrv_low</i> = '1' |                                             |  |  |  |  |

#### Table 10 Minimum HRV voltage (0x04)

| Register name: reg_hrv_check_lvl |               | Address: 0x05 | Default value mapped in E <sup>2</sup> PROM                                                                                                                                                                                                   |  |  |  |

|----------------------------------|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bits                             | Bit name      | Туре          | Description                                                                                                                                                                                                                                   |  |  |  |

| 7:4                              | -             | -             | Reserved                                                                                                                                                                                                                                      |  |  |  |

| 3:0                              | hrv_check_lvl | RW            | Minimum HRV short-cut current level to generate energy.<br>I <sub>hrv_check</sub> = (hrv_check_lvl+1) * 1μA<br>if I <sub>HRV</sub> < I <sub>hrv_check</sub> and <i>reg_v_hrv_cfg.hrv_check_vld</i> = '0' then <i>reg_status.hrv_low</i> = '1' |  |  |  |

#### Table 11 Minimum HRV short-cut current (0x05)

#### 6.2.3. TIMING CONFIGURATION

In addition to voltage level supervision, the user can select independent values for the frequency of supervision on LTS, STS and the harvester. The frequency influences the overall EM8502 power consumption and therefore its efficiency.

The STS and LTS measurement periods are set through the registers  $reg\_t\_st\_period$  and  $reg\_t\_tts\_period$ . The monitoring of the harvester however requires disconnecting the solar cell and the storages in order to measure the short-cut current. The duration of the disconnect time is configured through the  $reg\_t\_hrv\_meas$  register, whereas the measurement period is configured through the  $reg\_t\_hrv\_period$  register.

| Register value | t_hrv_meas | t_hrv_period | t_sts_period | t_lts_period | t_hrv_low_period | t_lts_hrv_low_period |

|----------------|------------|--------------|--------------|--------------|------------------|----------------------|

| 0x00           | 16 ms      | 256 ms       | 1 ms         | 1 ms         | 256 ms           | 2 ms                 |

| 0x01           | 32 ms      | 512 ms       | 2 ms         | 4 ms         | 512 ms           | 8 ms                 |

| 0x02           | 64 ms      | 1 s          | 8 ms         | 16 ms        | 1 s              | 32 ms                |

| 0x03           | 128 ms     | 2 s          | 16 ms        | 64 ms        | 2 s              | 128 ms               |

| 0x04           | 256 ms     | 4 s          | 32 ms        | 256 ms       | 4 s              | 512 ms               |

| 0x05           | 512 ms     | 8 s          | 64 ms        | 1 s          | 8 s              | 2 s                  |

| 0x06           | 1 s        | 16 s         | 128 ms       | 4 s          | 16 s             | 8 s                  |

| 0x07           | 2 s        | 32 s         | 256 ms       | 16 s         | 32 s             | 32 s                 |

#### Table 12 Timing Configuration

When entering in "HRV low mode" the monitoring on LTS and the harvester remains active, however the monitoring frequency can be adapted to this situation where the system cannot take energy anymore from the harvester source. The measurement period is then set in parameter t\_hrv\_low\_period. In this mode STS is not fed by the harvester anymore. If STS and LTS are not connected internally, STS will collapse. No monitoring is performed on STS.

## 6.3. POWER MANAGEMENT FUNCTIONS

The EM8502 controls four independent power supply outputs.

The VSUP power supply output is connected to STS when STS level is within the application voltage range ([v\_bat\_min:v\_apl\_max]) or to an LDO (when above v\_apl\_max) to regulate the output to a given value.

The three auxiliary supply outputs VAUX [0:2], are user configurable between STS and the internal LDO. It is possible to force the use of the LDO even though the STS voltage level is compatible with the application supply requirements.

During the boot phase – which corresponds to the set-up of the device – all the power supply outputs are floating. Once the set-up of the registers is completed the supply output values are determined by configuration registers  $reg_ldo_cfg.vsup_tied_low$  and  $reg_vaux_cfg.vaux[x]_cfg$ .

The main application power supply (VSUP) is intended to be connected to the application controller. When connected to the LDO its maximum power is limited as LDO is optimized for low consumption. The VSUP supply output is controlled by the  $reg_ldo_cfg$  register. The value of the LDO is configurable through  $reg_ldo_cfg.v_ulp_ldo$ . The LDO enable can be forced with  $reg_ldo_cfg.frc_ulp_ldo$ . In "sleep state", VSUP can be grounded ( $reg_ldo_cfg.vsup_tied_low = '1'$ ) or floating ( $reg_ldo_cfg.vsup_tied_low = '1'$ ) (see §6.4).

The individual configurability of the three auxiliary supply outputs allows the creation of different power domains for the external application. The auxiliary outputs are split into the supply and ground pins where all six outputs can be switched on/off independently. The behavior of the VAUX pins is controlled through the *reg\_vaux\_cfg* register. *reg\_vaux\_cfg.v\_aux\_ldo* controls the level of the single LDO connected to the three auxiliary supplies.

When switched on (reg\_pwr\_mgt.vaux[i]\_en = '1') the auxiliary supply output is controlled by reg\_vaux\_cfg.vaux[i]\_cfg.

Four possible settings are available to the user:

- 1) Force the connection to STS

- 2) Force the connection to the LDO

- 3) Use the automatic configuration permitting the auxiliary output to float when STS drops below v\_bat\_min

- 4) Use the automatic configuration grounding the auxiliary output when STS drops below v\_bat\_min

The automatic configuration of the auxiliary supplies is ensures that the auxiliary output voltage is kept within the application voltage range by auto-connecting the supply output to the LDO when STS voltage is exceeding the  $v_apl_max$  value.

When the power supply output is switched off (*reg\_pwr\_mgt.vaux[i]\_en* = '0'), its configuration is also controlled by the *reg\_pwr\_mgt.vaux[i]\_cfg* register. The output is grounded if *reg\_pwr\_mgt.vaux[i]\_cfg* is set to 3 (b11), otherwise it is kept floating.

When the LDO is used on VSUP or VAUX pins, changing the LDO settings does not generate over or under shoots on the output power supply terminals.

EM8502 offers the possibility to control the ground pin as part of the application, by connecting it to the ground of the EM8502 or letting it float. It is of particular interest when involving applications that are using  $I^2C$  communication through the pulls of the  $I^2C$  lines. The configuration of the VAUX\_GND pins is controlled through the *reg\_pwr\_mgt.vaux\_gnd[i] en* register.

|      | Register name: reg_ldo_cfg |      | Address: 0x0E                                                                                                                                                                                                                                                         | Default value mapped in E <sup>2</sup> PROM |  |

|------|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|

| Bits | Bit name                   | Туре | Descr                                                                                                                                                                                                                                                                 | iption                                      |  |

| 7    | vsup_tied_low              | RW   | When set to '1', connects VSUP pin to ground remains floating.                                                                                                                                                                                                        | when VSUP is disabled, otherwise VSUP       |  |

| 6:4  | v_vaux_ldo                 | RW   | VAUX LDO regulated voltage selection<br>• "000" (0) 1.2 V<br>• "001" (1) 1.55 V<br>• "010" (2) 1.65 V<br>• "011" (3) 1.8 V<br>• "100" (4) 2.0 V<br>• "101" (5) 2.2 V<br>• "110" (6) 2.4 V<br>• "111" (7) 2.6 V                                                        |                                             |  |

| 3    | frc_ulp_ldo                | RW   | Force ULP LDO on as soon as V <sub>STS</sub> > <b>v_bat_r</b>                                                                                                                                                                                                         | min_hi                                      |  |

| 2:0  | v_ulp_ldo                  | RW   | ULP LDO regulated voltage selection         • "000" (0)       1.2 V         • "001" (1)       1.55 V         • "010" (2)       1.65 V         • "011" (3)       1.8 V         • "100" (4)       2.0 V         • "101" (5)       2.2 V         • "111" (7)       2.6 V |                                             |  |

Table 13 VSUP output supply and LDOs configuration register (0x0E)

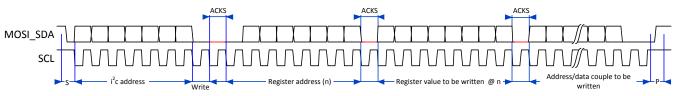

Table 14 "HRV low" mode power switch configuration register (0x0F)

|      | Register name: reg_vaux_cfg |      | Address: 0x10                                                                                                                                                                                                                                                                                                                                                                                                       | Default value mapped in E <sup>2</sup> PROM |  |  |

|------|-----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Bits | Bit name                    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |  |  |

| 7:6  | -                           | -    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |  |  |

| 5:4  | vaux2_cfg                   |      | Configuration of VAUX[2] pin     "00" (0) Constantly connected to STS     "01" (1) Constantly connected to the LDO     "10" (2) Automatic configuration – floating when below V <sub>STS</sub> < <b>v_bat_min</b> "11" (3) Automatic configuration – grounded when below V <sub>STS</sub> < <b>v_bat_min</b> If VAUX[2] is disconnected – VAUX[2] is connected to ground if the value is "11", otherwit is floating |                                             |  |  |

| 3:2  | vaux1_cfg                   | RW   | Configuration of VAUX[1] pin – same as for VAUX[2] pin                                                                                                                                                                                                                                                                                                                                                              |                                             |  |  |

| 1:0  | vaux0_cfg                   | RW   | Configuration of VAUX[0] pin – same as for VA                                                                                                                                                                                                                                                                                                                                                                       | AUX[2] pin                                  |  |  |

#### Table 15 Auxiliary supply configuration register (0x10)

| Register name: reg_vaux_gnd_cfg |               |      | Address: 0x11                                                                                                                      | Default value mapped in E <sup>2</sup> PROM |  |  |

|---------------------------------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Bits                            | Bit name      | Туре | Description                                                                                                                        |                                             |  |  |

| 7:3                             | -             | -    | Reserved                                                                                                                           |                                             |  |  |

| 2                               | vaux_gnd2_cfg | RW   | <ul> <li>'1' Auto disconnect when V<sub>STS</sub> not within [v_bat_min v_apl_max]</li> <li>'0' Fully manual connection</li> </ul> |                                             |  |  |

| 1                               | vaux_gnd1_cfg | RW   | Configuration of VAUX_GND[1] pin – same as for VAUX_GND [2] pin                                                                    |                                             |  |  |

| 0                               | vaux_gnd0_cfg | RW   | Configuration of VAUX_GND[0] pin – same as for VAUX_GND[2] pin                                                                     |                                             |  |  |

Table 16 Auxiliary ground pins configuration register (0x11)

# EM8502

|      | Register name: reg_pwr_mgt |      | Address: 0x19                                                                                                              | Value at start-up mapped in E <sup>2</sup> PROM             |

|------|----------------------------|------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Bits | Bit name                   | Туре | Descr                                                                                                                      | iption                                                      |

| 7    | -                          | -    | To be written always to '0'                                                                                                |                                                             |

| 6    | vaux_gnd2_en               | RW   | Enable the VAUX_GND[2] connection (see <i>reg_vaux_gnd_cfg.vaux_gnd2_cfg</i> ) when V <sub>STS</sub> <b>v_bat_min_hi</b>   |                                                             |

| 5    | vaux_gnd1_en               | RW   | Enable the VAUX_GND[1] connection (see <i>reg_vaux_gnd_cfg.vaux_gnd0_cfg</i> ) when V <sub>STS</sub> > <b>v_bat_min_hi</b> |                                                             |

| 4    | vaux_gnd0_en               | RW   | Enable the VAUX_GND[0] connection (see <i>reg_vaux_gnd_cfg.vaux_gnd0_cfg</i> ) when V <sub>STS</sub> > <b>v_bat_min_hi</b> |                                                             |

| 3    | vaux2_en                   | RW   | Enable the VAUX[2] connection (see reg_vau                                                                                 | xcfg.vaux2_cfg) when V <sub>STS</sub> > <b>v_bat_min_hi</b> |

| 2    | vaux1_en                   | RW   | Enable the VAUX[1] connection (see reg_vauxcfg.vaux1_cfg) when V <sub>STS</sub> > v_bat_min_hi                             |                                                             |

| 1    | vaux0_en                   | RW   | Enable the VAUX[0] connection (see <i>reg_vauxcfg.vaux0_cfg</i> ) when V <sub>STS</sub> > <b>v_bat_min_hi</b>              |                                                             |

| 0    | sleep_vsup                 | RW   | Enable the VSUP "sleep state" - disconnects                                                                                | VSUP for <b>t_sleep_vsup</b> interval                       |

#### Table 17 Power switch enable register (0x19)

## 6.4. SLEEP MODE AND WAKE-UP FUNCTIONS

In addition to the direct control of the power supply outputs the EM8502 supports stopping supplying the application (switching off VSUP) for a given time interval to allow very low consumption modes. When enabled, the auxiliary supplies are kept in the same state as before entering in the "sleep state". The "sleep state" is not a functional mode of the power management unit, as the device is still working according to the configuration parameters set and is only acting on the state of the VSUP supply output.

The "sleep state" can also be interrupted (VSUP is connected again on STS or on the LDO according to the settings of the VSUP power switch see Table 13) by setting the WAKE\_UP pin to a level above  $V_{ih_wk}$ .

During "sleep state" the serial interface is disabled.

To avoid false wake-up detection, a debouncing logic is connected to the WAKE\_UP pin. The debouncer function is enabled by default (factory default value on  $E^2PROM$ ), and can be disabled by setting the *reg\_ext\_cfg. wake\_up\_deb\_en* to '0'. The wake-up is sensitive to the edge configured in *reg\_ext\_cfg.wake\_up\_edge\_cfg*. It is not permitted to set *reg\_ext\_cfg.wake\_up\_edge\_cfg* = "00".

|      | Register name: reg_ext_cfg |      | Address: 0x13                                                                                                                                                                        | Default value mapped in E <sup>2</sup> PROM |  |  |

|------|----------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Bits | Bit name                   | Туре | Description                                                                                                                                                                          |                                             |  |  |

| 7    | sda_slopectrl              | RW   | <ul> <li>MOSI_SDA pad slope control</li> <li>'0' for standard and fast I2C mode, and high speed mode if VSUP &lt; 1.8V</li> <li>'1' for high speed mode if VSUP &gt; 1.8V</li> </ul> |                                             |  |  |

| 6    | wake_up_deb_en             | RW   | When at '1' the wake-up debouncer is enabled                                                                                                                                         |                                             |  |  |

| 5:4  | wake_up_edge_cfg           | RW   | "00" (0x0): Forbidden<br>"01" (0x1): wake-up on falling edge<br>"10" (0x2): wake-up on rising edge<br>"11" (0x3): wake-up on both edge                                               |                                             |  |  |

| 3    | usb_frc_hrv_low_hiz        | RW   | See Table 24 USB Configuration Register (0x13)                                                                                                                                       |                                             |  |  |

| 2    | usb_frc_bat_low_hiz        | RW   | See Table 24 USB Configuration Register (0x13)                                                                                                                                       |                                             |  |  |

| 1:0  | usb_crt_src_sel            | RW   | See Table 24 USB Configuration Register (0                                                                                                                                           | x13)                                        |  |  |

#### Table 18 Wake-up terminal configuration register (0x13)

The "sleep state" duration is controlled through a 24-bit counter (*reg\_t\_sleep\_vsup*[23:0]). VSUP supply can be interrupted for up to 4 hours, with a granularity of 1 ms.

#### t\_sleep\_vsup = reg\_t\_sleep\_vsup[23:0]/1000 seconds

When VSUP is in "sleep state" it is possible to ground VSUP to create a known voltage level on the main controller supply, by setting reg\_ldo\_cfg.vsup\_tied\_low to '1' (see above in page 13).

#### The VSUP "sleep state" is enabled by setting reg\_pwr\_mgt.sleep\_vsup to '1' (see Table 17 bit 0).

# EM8502

| Register name: reg_t_sleep_vsup_lo |                 | Address: 0x14 Default value mapped in E <sup>2</sup> |                                                 |  |

|------------------------------------|-----------------|------------------------------------------------------|-------------------------------------------------|--|

| Bits                               | Bit name        | Туре                                                 | Description                                     |  |

| 7:0                                | t_sleep_vsup_lo | RW                                                   | Sleep counter duration – least significant byte |  |

#### Table 19 VSUP "sleep state" counter time-out Least significant byte (0x14)

| Reg  | Register name: reg_t_sleep_vsup_mid |      | Address: 0x15 Default value mapped in E <sup>2</sup> P |  |

|------|-------------------------------------|------|--------------------------------------------------------|--|

| Bits | Bit name                            | Туре | Description                                            |  |

| 7:0  | t_sleep_vsup_mid                    | RW   | Sleep counter duration – byte 2                        |  |

#### Table 20 VSUP "sleep state" counter time-out middle significant byte (0x15)

| Register name: reg_t_sleep_vsup_hi |                 | Address: 0x16 Default value mapped in E |                                                |  |

|------------------------------------|-----------------|-----------------------------------------|------------------------------------------------|--|

| Bits                               | Bit name        | Туре                                    | Description                                    |  |

| 7:0                                | t_sleep_vsup_hi | RW                                      | Sleep counter duration – most significant byte |  |