# OPTIMIZED Bluetooth 5.0 Low-Energy Companion or SoC

# **Description**

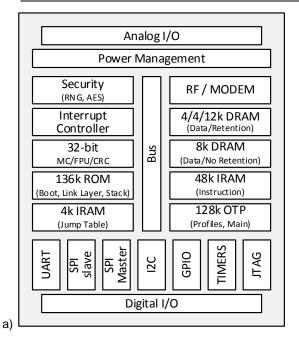

The EM9304 is a tiny, low-power, integrated circuit (IC) optimized for *Bluetooth*® 5.0 low energy enabled products. The flexible architecture of the EM9304 allows it to act as a companion IC to any ASIC or MCU-based product, or as a complete System-on-Chip (SoC). Custom applications can execute from one-time-programmable (OTP) memory, and digital peripherals (SPI or I2C) can be used to interface with external devices such as sensors, memory, display, or touch drivers. A floating point unit can be exploited to implement advanced algorithms such as sensor fusion.

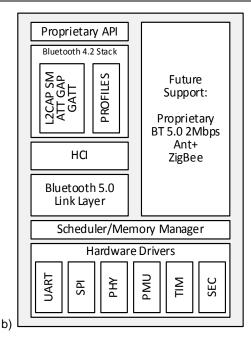

Included in ROM is a Bluetooth 5.0 link layer with a Host Controller Interface (HCI), a Bluetooth stack with proprietary Application Controller Interface (ACI), several profiles, and over-the-air firmware (FOTA) updating routines. The Bluetooth low energy controller and host can be configured to support up to eight simultaneous connections. Secure connections and extended packet length are also supported.

The EM9304 includes a sophisticated on-chip power management system with automatic configuration for 1.5V or 3V batteries. Current consumption is minimized for all modes of the application utilizing an efficient scheduler and memory manager. Several memory configuration options allow for optimum performance for any given application. A stable, low-power sleep oscillator (RC or crystal based) minimizes power consumption while in a connected state.

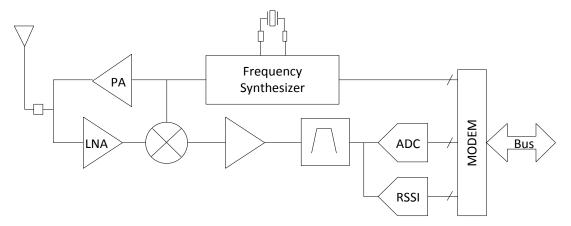

The EM9304 features a state-of-the-art 2.4GHz transceiver: an extremely low-power receiver with excellent sensitivity/selectivity, and a programmable transmitter for optimized output power and current consumption.

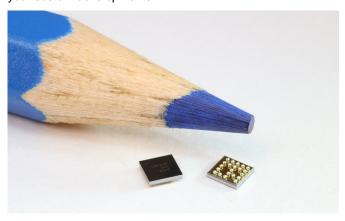

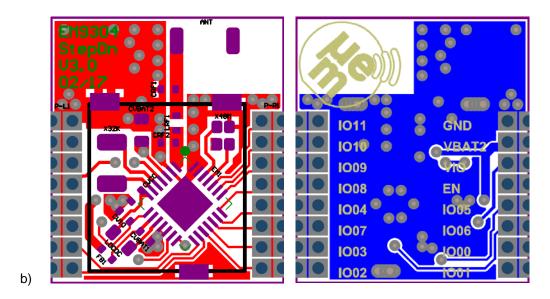

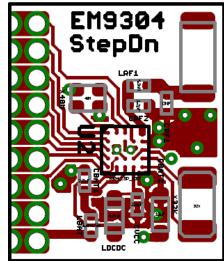

The PCB footprint and cost is minimized with a very low external component count and several package options. The circuit is offered in a WLCSP25 wafer level chip-scale package, a plastic QFN-28 package, and bare die/ wafer form. The device and reference design is qualified over the industrial temperature range.

Customer support for PCB design, and FCC/CE certification are available. A hardware and software development kit are available, including commercially available tools with IDE and debugger. A website and forum are also available to help with your custom developments.

## **Main Features**

System-on-Chip:

Energy efficient, industry standard, ARC EM4, 32-bit MCU running at 24MHz

Floating-point unit for sensor processing

136kB ROM including link layer and stack

128kB OTP for parameters, profiles, and applications

24MHz execution speed

48kB instruction RAM and 28kB data RAM

4, 8, or 20kB with selectable data retention

Universal, sleep, and protocol timers

I2C and SPI master interfaces

Up to 12 GPIO

Bluetooth 5.0 Low Energy Technology:

BT 5.0 Controller Subsystem (QD ID 93999)

Bluetooth stack (QD ID 84268) in ROM

SPI and UART HCI/ACI Transport Layers

Up to eight simultaneous connections supported

Extended PDU length and enhanced security

Security Features:

True Random Number Generator

AES-128 Hardware Encryption Engine

Key Generation (ECC-P256)

Firmware Over-the-Air Updating

Per application, function, or configuration

Sophisticated Power Management System:

Digital step-up/down DCDC operation

Supports 1.5V and 3.0V batteries

Scheduler and memory manager

Low frequency RC or crystal oscillator time base

Low Current Consumption at 3V:

3.0mA typical peak receiver current

5.2mA typical peak transmitter current at 0.4dBm

1.0μA connected sleep mode

5nA chip disable mode

High Performance RF:

-94dBm Bluetooth low energy receiver sensitivity for 1Mpbs operation and 37 byte payload

-34 to +6.1dBm transmitter output power range

Low Component Count and Cost:

3 DC caps, 1 DCDC coil, 1 ferrite bead Single ended 50Ω antenna pin (no balun) 48MHz XTAL, 32kHz XTAL (optional)

Packaging:

QFN-28 (4x4mm), WLCSP25, and bare-die/wafer Industrial Operating Temperature Range: -40C to +85C Customer Support:

Hardware, software development kits

FCC/CE certification support

Forum for hardware and software support

# **Typical Applications**

Bluetooth low energy applications such as:

Beacons

Wearables and Sports Equipment

Healthcare Monitoring

Remote Sensing

Motion and Tracking Devices

Home Automation

Light Control Applications

Wireless Mice and Keyboards

Alarms and Security System

Enabled by the mobile phone as access-point to the Internet.

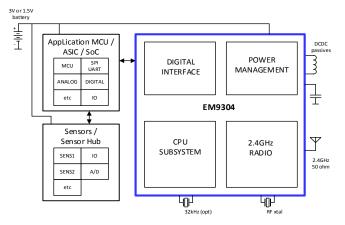

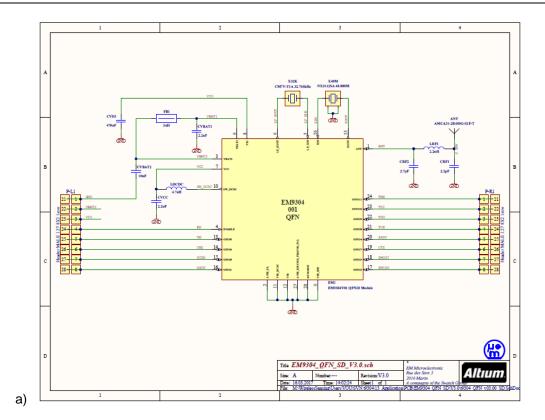

# **Typical Application Diagrams**

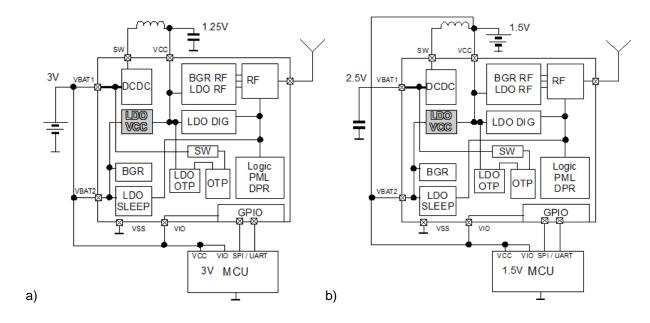

The EM9304 is the ideal Bluetooth low energy companion IC for any MCU or ASIC application, as illustrated in Figure 1. It may be easily connected with:

- standard 3V MCU's within the very rich catalog of any microprocessor vendor;

- standard 1.5V MCU's such as ultra-low-power watch microprocessors from EM Microelectronic;

- any custom sensor processing ASIC for customers requiring a simple add-on function.

Figure 1: Typical Application Schematic – Bluetooth Low-Energy Companion IC to any MCU or ASIC

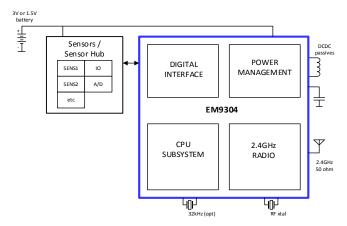

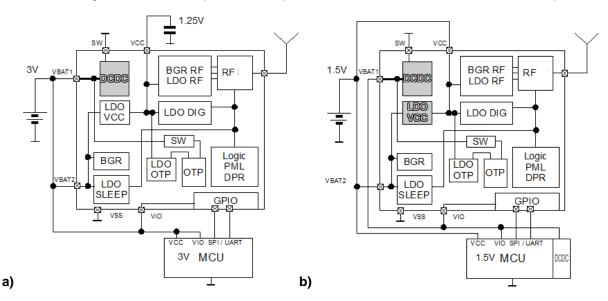

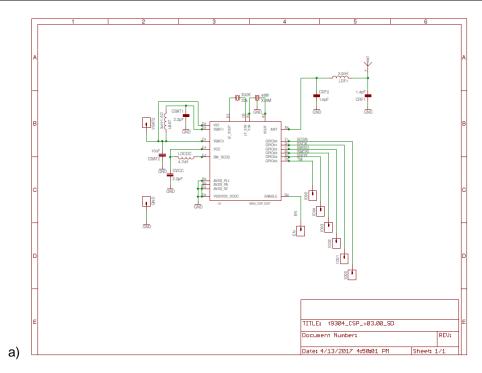

The EM9304 is a flexible solution which may also be used without an external MCU for simple applications such as beacons. As illustrated in Figure 2, it may be directly connected to external digital sensors which may exploit the EM9304's internal 32-bit processing capability, or with sensor hubs such as from EM's SENtral platform. Other applications using A/D converters, EEPROMs, display and/or touch interfaces can also be implemented.

The EM9304 can be supplied from a 3V battery (e.g. Lithium coin-cell). In such case, the DCDC converter is put into step-down configuration. The EM9304 can also be supplied from a 1.5V battery (e.g. Alkaline, Silver-Oxide, or Zinc-Air single cells). In such case, the DCDC converter is put into step-up configuration.

Finally, configurations are also possible without the DCDC converter (no inductor required), for systems already with

power management, or for systems that require the lowest bill of materials.

Figure 2: Typical Application Schematic – EM9304 Connected With Digital Sensors / Sensor Hubs

# **Package Information**

The versions below are considered standards and should be readily available. Please make sure to give the complete part number when ordering.

WLCSP25, 5x5 array, 0.4mm pitch, 2.3x2.2mm

QFN-28, 0.4mm pitch, 4x4mm

Bare die in wafer format

Please contact EM Microelectronic-Marin S.A. for more information.

# **Product and Developer Support**

The following product support is available:

Hardware Development Kit (DVK)

Software Development Kit (SDK)

Getting Started guide and PC Tools

Integrated Development Environment (IDE) for ARC Metaware and MetawareLite Tools

Reference designs with schematics, PCB layouts, and bill-of-materials

Developer forum for hardware and software support

www.emdeveloper.com

PCB Antenna Design Support

FCC/CE Test Support

The Bluetooth®word mark and logos are registered trademarks owned by the Bluetooth SIG, Inc. and any use of such marks by EM Microelectronic is under license. Other trademarks and trade names are those of their respective owners.

# **Table of Contents**

| 1 | Overview                                                     | 6        |

|---|--------------------------------------------------------------|----------|

|   | 1.1 Introduction                                             | 6        |

|   | 1.2 Chip Architecture                                        | 7        |

|   | 1.3 RF Description                                           |          |

|   | 1.4 Power Management Description                             |          |

|   | 1.5 Operating Modes                                          |          |

|   | 1.6 Pin Description                                          |          |

|   | 1.7 GPIO Configuration                                       |          |

|   | 1.8 QFN Reference Schematics and External Components         |          |

|   | 1.9 WLCSP Reference Schematics and External Components       | 14       |

|   | 1.10 Related Documents                                       | 15       |

| 2 | Electrical Specifications                                    | 16       |

|   | 2.1 Absolute Maximum Ratings                                 |          |

|   | 2.2 Handling Procedures                                      |          |

|   | 2.3 General Operating Conditions                             |          |

|   | 2.4 Electrical Characteristics                               | 17       |

|   | 2.5 DC Characteristics                                       |          |

|   | 2.5.1 DCDC Step-Down Configuration                           |          |

|   | 2.5.2 DCDC Step-Up Configuration                             | 17       |

|   | 2.5.3 DCDC Off Configuration and External DCDC Configuration | 1.9      |

|   | 2.6 GPIO Characteristics                                     | 19       |

|   | 2.6.1 GPIO Pin Characteristics                               |          |

|   | 2.6.3 SPI Timing                                             |          |

|   | 2.7 Power Management Characteristics                         |          |

|   | 2.7.1 Low Frequency Crystal Oscillator Specifications        | ∠ı<br>21 |

|   | 2.7.1 Low Frequency Crystal Oscillator Specifications        | ∠ı<br>21 |

|   | 2.7.2 Timing Characteristics                                 | ∠ı       |

|   | 2.8.1 General RF Characteristics                             | ∠ı       |

|   | 2.8.2 High Frequency Crystal Oscillator Specifications       |          |

|   | 2.8.3 Transmitter Characteristics                            | 22       |

|   | 2.8.4 Receiver Characteristics                               |          |

| 2 | Functional Description                                       |          |

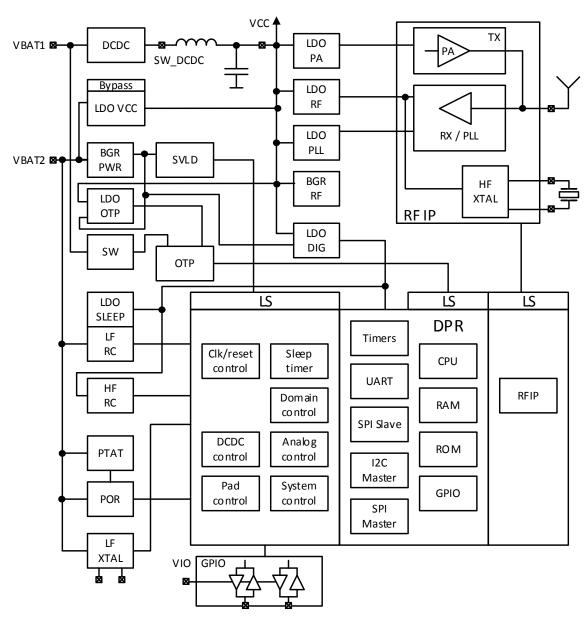

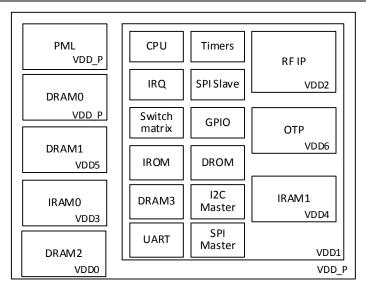

| 3 | 3.1 Block Diagram                                            |          |

|   | 3.1.1 Digital Processing                                     | 24<br>25 |

|   | 3.1.2 CPU                                                    |          |

|   | 3.1.3 Memories                                               |          |

|   | 3.1.4 Peripherals                                            |          |

|   | 3.1.5 Applications and Patch Loading                         |          |

|   | 3.1.6 Security                                               |          |

|   | 3.2 Peripherals                                              |          |

|   | 3.2.1 I2C Master                                             |          |

|   | 3.2.2 SPI Master                                             |          |

|   | 3.2.3 UART                                                   |          |

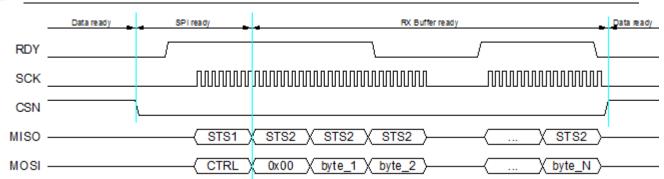

|   | 3.2.4 SPI Slave                                              |          |

|   | 3.2.5 GPIO                                                   |          |

|   | 3.2.6 Timers                                                 | 34       |

|   | 3.3 Power Management                                         |          |

|   | 3.3.1 Supply Domains                                         |          |

|   | 3.3.2 Logic Power Domains                                    |          |

|   | 3.3.3 Supply Monitoring                                      |          |

|   | 3.3.4 Chip Disable                                           |          |

|   | 3.3.5 Reset Structure                                        |          |

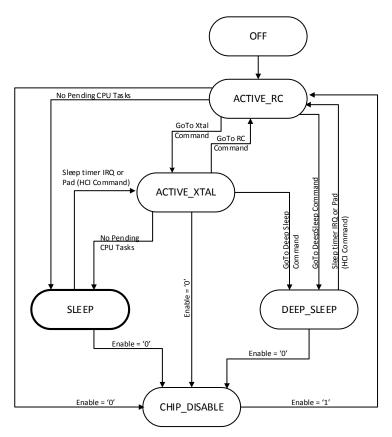

|   | 3.4 Operating Modes                                          | 37       |

|   | 3.4.1 Mode Descriptions                                      | 37       |

|   | 3.4.2 Mode Transitions                                       | 38       |

|   | 3.5 Clock Structure                                          | 39       |

|   | 3.5.1 LF XTAL Modes                                          | 39       |

|   | 3.5.2 LF Clock Calibration                                   | 39       |

| 4 | Ordering information                                         |          |

|   | 4.1 Ordering information                                     | 40       |

|   | 4.2 Pin List                                                 |          |

|   | 4.3 QFN Package Marking                                      |          |

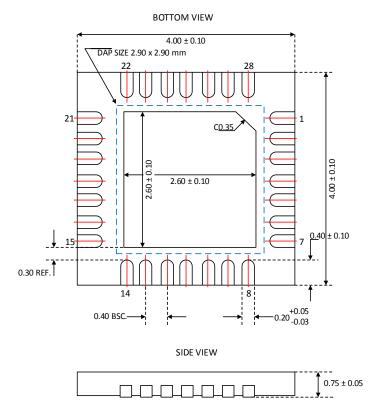

|   | 4.4 QFN Package Information                                  | 41       |

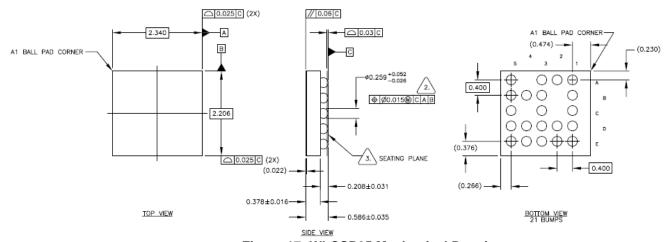

|   | 4.5 WLCSP Package Information                                |          |

| _ | 4.6 WLCSP Package Marking                                    |          |

| 5 | Embedded Software                                            |          |

|   | 5.1 Overview                                                 | 43       |

| 5.2 Hardware Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.2.1 Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.2.2 Embedded Software Memory Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

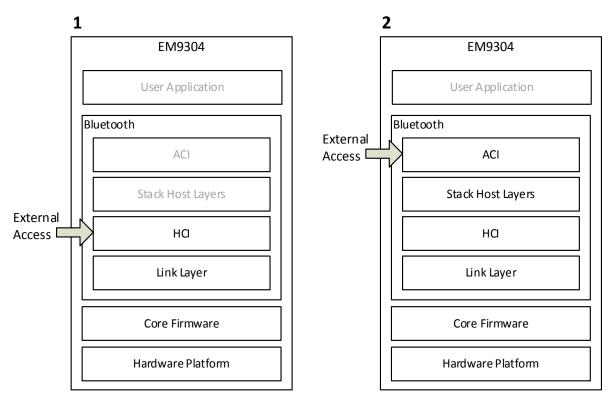

| 5.3 Software Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.3.1 Application Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 5.3.2 Hardware Abstraction Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 5.4 Production Test Mode (PTM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 5.5 Software Configuration Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 5.6 Vendor Specific HCI Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 5.6.1 EM_SetPublicAddress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.6.2 EM_SetUartBaudRate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.6.3 EM_TransmitterTest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.6.4 EM_TransmitterTestEnd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 5.6.5 EM_ReadAtAddress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 5.6.6 EM_ReadContinue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 5.6.7 EM_WriteAtAddress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 5.6.8 EM_WriteContinue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 5.6.9 EM_SetPowerModeEx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 5.6.10 EM_SetRfActivitySignalEx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 5.6.11 EM_SetRfPowerLevelEx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 5.6.12 EM_WritePatchStart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.6.13 EM_WritePatchContinue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 5.6.14 EM_WritePatchAbort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.6.15 EM_SetClockSource                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.6.16 EM_SetMemoryMode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61       |

| 5.6.17 EM_GetMemoryUsage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.6.18 EM_SetSleepOptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62       |

| 5.6.19 EM_SvldMeasurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62       |

| 5.6.20 EM_SetEventMask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63       |

| 5.6.21 EM_CpuReset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63       |

| 5.6.22 EM_CalculateCrc32Ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 5.6.23 EM_PatchQuery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| 5.7 Vendor Specific Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 5.7.1 EM_ActiveStateEntered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 5.7.2 EM_TestModeEntry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66       |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66<br>66 |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66       |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66<br>   |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces  Table 4: Recommended Component List for the Reference Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces  Table 4: Recommended Component List for the Reference Design  Table 5: Absolute Maximum Ratings  Table 6: General Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces  Table 4: Recommended Component List for the Reference Design  Table 5: Absolute Maximum Ratings  Table 6: General Operating Conditions  Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces  Table 4: Recommended Component List for the Reference Design  Table 5: Absolute Maximum Ratings  Table 6: General Operating Conditions  Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V  Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V  Table 9: GPIO Pin Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces  Table 4: Recommended Component List for the Reference Design  Table 5: Absolute Maximum Ratings  Table 6: General Operating Conditions  Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V  Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V  Table 9: GPIO Pin Characteristics  Table 10: I2C Output Pin Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options  Table 2: Typical Battery Types  Table 3: Digital Interfaces  Table 4: Recommended Component List for the Reference Design  Table 5: Absolute Maximum Ratings  Table 6: General Operating Conditions  Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V  Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V  Table 9: GPIO Pin Characteristics  Table 10: I2C Output Pin Characteristics  Table 11: I2C Capable GPIO Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

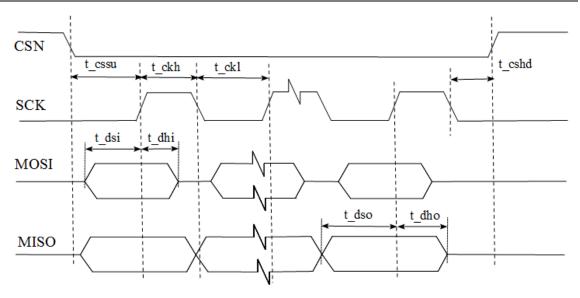

| 5.7.3 EM_HalNotification 5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options Table 2: Typical Battery Types Table 3: Digital Interfaces Table 4: Recommended Component List for the Reference Design Table 5: Absolute Maximum Ratings Table 6: General Operating Conditions Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V Table 9: GPIO Pin Characteristics Table 10: I2C Output Pin Characteristics Table 11: I2C Capable GPIO Timing Characteristics Table 12: SPI Timing Specification for VBAT > 1.9V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 5.7.3 EM_HalNotification 5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options Table 2: Typical Battery Types Table 3: Digital Interfaces Table 4: Recommended Component List for the Reference Design Table 5: Absolute Maximum Ratings Table 6: General Operating Conditions Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V. Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V. Table 9: GPIO Pin Characteristics Table 10: I2C Output Pin Characteristics Table 11: I2C Capable GPIO Timing Characteristics Table 12: SPI Timing Specification for VBAT > 1.9V. Table 13: SPI Timing Specification for VBAT < 1.9V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 5.7.3 EM_HalNotification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 5.7.3 EM_HalNotification 5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options Table 2: Typical Battery Types Table 3: Digital Interfaces Table 4: Recommended Component List for the Reference Design Table 5: Absolute Maximum Ratings Table 6: General Operating Conditions Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V Table 9: GPIO Pin Characteristics Table 10: I2C Output Pin Characteristics Table 11: I2C Capable GPIO Timing Characteristics Table 12: SPI Timing Specification for VBAT > 1.9V Table 13: SPI Timing Specification for VBAT < 1.9V Table 14: Low Frequency Crystal Oscillator Specifications Table 15: Start-Up Characteristics                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 5.7.3 EM_HalNotification 5.8 Hardware Error Event Codes  List of Tables  Table 1: DCDC Configuration Options Table 2: Typical Battery Types Table 3: Digital Interfaces Table 4: Recommended Component List for the Reference Design Table 5: Absolute Maximum Ratings Table 6: General Operating Conditions Table 7: DC Characteristics, DCDC Step-Down Configuration, VBAT2=3.0V Table 8: DC Characteristics, DCDC Step-Up Configuration, VBAT2=1.5V Table 9: GPIO Pin Characteristics Table 10: I2C Output Pin Characteristics Table 11: I2C Capable GPIO Timing Characteristics Table 12: SPI Timing Specification for VBAT > 1.9V Table 13: SPI Timing Specification for VBAT < 1.9V Table 14: Low Frequency Crystal Oscillator Specifications Table 15: Start-Up Characteristics Table 16: Timing Characteristics                                                                                                                                                                                                                                                                                                                                                 |          |

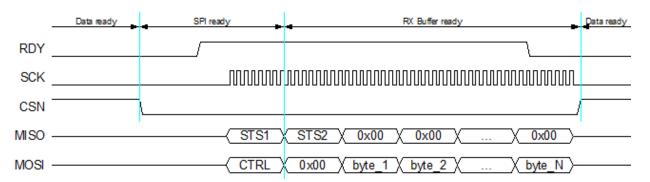

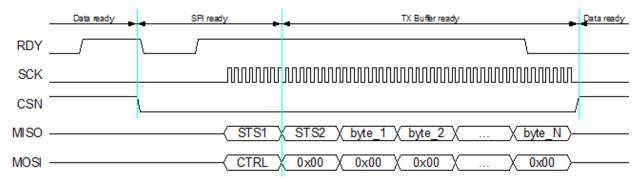

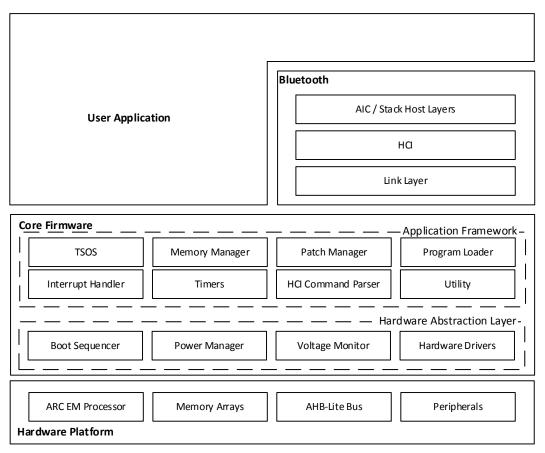

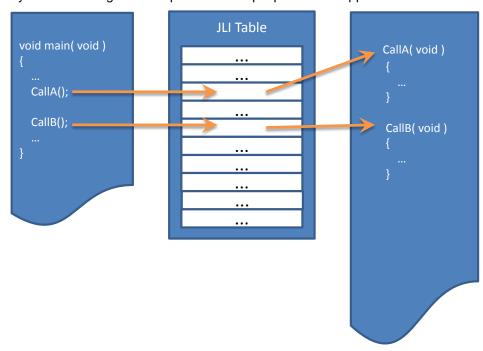

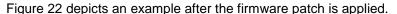

| 5.7.3 EM_HalNotification  5.8 Hardware Error Event Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |