# 1 kbit Read/Write, ISO 18000-6C / EPC C-1 G-2 Passive / Battery-assisted Contactless IC

## **Description**

EM4324 is a long range passive / battery-assisted UHF RFID tag IC compliant with the ISO 18000-6C / EPCglobal Class-1 Generation-2 protocol. The chip offers an advanced feature set (EPC+) leading to a performance beyond that of standard Gen2 chips. Battery-assisted, EM4324 offers superior reading range and reliability compared to purely passive RFID solutions. The battery-assisted mode is tailored to harsh environment applications where other passive UHF solutions fail e.g. in the presence of water or metal.

The EM4324 current consumption has been optimized to maximize battery lifetime. Even if the battery is flat, the chip continues to operate and communicate with the reader in passive mode.

The memory size is 1024 bits enabling support of ISO or EPC data structures. Each chip is delivered with a 64-bit Unique Identifier to ensure full traceability.

The EM4324 includes a tamper detection circuit to support E-seal applications. Tamper detection can be implemented using a simple continuity loop, with heat sensitive fuse wire, with sensors having both high and low impedance states, or with external devices controlling an electronic switch such as a MOSFET.

### **Applications**

- Supply chain management

- □ Tracking and tracing

- Containers identification

- Access control

- Asset control

- □ E-seals

#### **Features**

- ISO 18000-6C compliant

- EPC Class-1 Gen-2 compliant

- 1024-bit non-volatile memory

- □ 720-bit user's free memory

- 96-bit EPC numbers supported

- 64-bit manufacturer-programmed Unique Identifier (TID / UID)

- ☐ Forward link data rates: 40 to 160 kbit/s

- □ Return link data rates: 40 to 640 kbit/s

- □ Tamper detection

- Battery assistance mode for unsurpassed reading range and reading reliability

- Rectifier that allows passive operation in case the battery is flat or not present

- □ Support of near-field mode enabling reading e.g. through water

- Support of parallel-inductance matching for improved matching

- □ 32-bit password-protected Kill command

- 32-bit password-protected Access command

- ☐ Anti-tearing feature to prevent malicious unlocking

- ☐ Extended temperature range (-40°C to +85°C)

- Available also in TSSOP-8 package

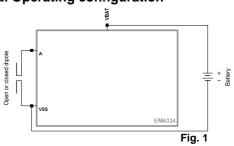

# **Typical Operating configuration**

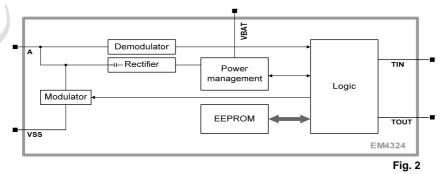

# **IC Block Diagram**

## **Absolute Maximum Ratings**

| Parameters                                              | Symbol                | Min.                 | Max.                 | Unit |

|---------------------------------------------------------|-----------------------|----------------------|----------------------|------|

| Operating temperature                                   | T <sub>OP</sub>       | -40                  | 85                   | °C   |

| Storage temperature                                     | T <sub>STORE</sub>    | -50                  | 150                  | °C   |

| Voltage on pad A                                        | V <sub>A_ABS</sub>    | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +3.6 | V    |

| Voltage on pad VBAT                                     | V <sub>BAT_ABS</sub>  | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +3.6 | V    |

| Voltage on pad VSS                                      | V <sub>SS</sub>       | -                    | -                    | V    |

| RF power at pad A                                       | P <sub>A_ABS</sub>    |                      | 20                   | dBm  |

| Voltage on<br>pad TST,<br>TST2, TIN,<br>TOUT            | V <sub>TST_ABS</sub>  | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +3.6 | ٧    |

| DC current into pads except pad A                       | I <sub>ABS</sub>      | -98                  | 98                   | mA   |

| DC current into pad A                                   | I <sub>A_ABS</sub>    | -20                  | 20                   | mA   |

| Electrostatic<br>discharge on<br>pad A <sup>1)</sup>    | V <sub>ESD_A</sub>    | -1250                | 1250                 | V    |

| Electrostatic<br>discharge on<br>pad VBAT <sup>1)</sup> | V <sub>ESD_VBAT</sub> | -2000                | 2000                 | V    |

Stresses above these listed maximum ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

# **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level.

**Operating Conditions**

| Parameters                                                                     | Symbol           | Min. | Max. | Unit |

|--------------------------------------------------------------------------------|------------------|------|------|------|

| Operating temperature                                                          | T <sub>OP</sub>  | -40  | +85  | င့   |

| Battery operating voltage (between VBAT and VSS)                               | V <sub>BAT</sub> | 1.25 | 3.3  | V    |

| RF power at pad A (antenna impedance conjugate complex to Z <sub>A_PAS</sub> ) | P <sub>A</sub>   |      | 5    | dBm  |

| RF carrier frequency                                                           | f <sub>A</sub>   | 860  | 960  | MHz  |

Table 2

Note 1: Human Body Model (HBM; 100pF; 1.5kOhm) with reference to substrate VSS.

# **Electrical Characteristics**

| Parameters                                                                                                                                                | Symbol               | Conditions                                                                                                      | Min. | Тур.                          | Max.       | Unit              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|------|-------------------------------|------------|-------------------|

| Battery operating voltage for read                                                                                                                        | $V_{BAT\_RD}$        | V <sub>BAT</sub> > 1.4V during<br>100µs at T=25°C<br>when applying V <sub>BAT</sub>                             | 1.25 |                               | 3.3        | V                 |

| Battery operating voltage for write                                                                                                                       | $V_{BAT\_WR}$        |                                                                                                                 | 2    |                               | 3.3        | V                 |

| Average battery current in Sleep mode                                                                                                                     | I <sub>BAT_S_A</sub> | V <sub>BAT</sub> =1.5V, T=25°C<br>V <sub>BAT</sub> = 3V, T=25°C                                                 |      | 0.6<br>0.9                    | 0.9<br>1.4 | uA<br>uA          |

| Average battery current in Ready state                                                                                                                    | I <sub>BAT_R_A</sub> | V <sub>BAT</sub> =1.5V, T=25°C<br>V <sub>BAT</sub> = 3V, T=25°C                                                 |      | 11<br>22                      | 25<br>40   | uA<br>uA          |

| Depth to which the carrier is modulated                                                                                                                   | K <sub>M</sub>       |                                                                                                                 | 65   |                               | 100        | %                 |

| Input impedance (between A and VSS) below passive activation threshold <sup>1</sup> ; to be used for antenna matching optimized for battery-assisted mode | Z <sub>A_BAT</sub>   | battery-assisted<br>mode<br>$P_{DUT}$ =-27dBm<br>T = 25°C<br>$f_A = 868MHz$<br>$f_A = 915MHz$<br>$f_A = 956MHz$ |      | 11-j164<br>11-j155<br>11-j148 |            | $\Omega$ $\Omega$ |

<sup>&</sup>lt;sup>1</sup> The activation threshold is defined as the RF power level above which the chip starts operating and is equal to or lower than the read sensitivity

**Electrical Characteristics (continued)**

| Parameters                                                                                                                                     | Symbol               | Conditions                                                                                                                | Min. | Тур.                          | Max. | Unit                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|------|----------------------------|

| Input impedance (between A and VSS) above passive activation threshold; to be used for antenna matching optimized for passive mode             | Z <sub>A_PAS</sub>   | passive mode (no battery) $P_{DUT}=-10dBm$ $T=25^{\circ}C$ $f_{A}=868MHz$ $f_{A}=915MHz$ $f_{A}=956MHz$                   |      | 19-j188<br>18-j178<br>17-j170 |      | Ω<br>Ω<br>Ω                |

| TSSOP-8 input impedance (between A and VSS) below passive activation threshold <sup>2</sup> (impedance only valid for TSSOP-8 package option!) | Z <sub>A_TSSOP</sub> | $P_{DUT}$ =-27dBm<br>T = 25°C<br>$f_A = 868MHz$<br>$f_A = 915MHz$                                                         | 4    | 21-j145<br>22-j135            |      | $\Omega$                   |

| Input impedance (between A and VSS) when modulator is on                                                                                       | Z <sub>A_ON</sub>    | battery-assisted mode ( $V_{BAT}$ =1.1V) $P_{DUT}$ =-27dBm $T = 25^{\circ}C$ $f_A = 868MHz$ $f_A = 915MHz$ $f_A = 956MHz$ |      | 62-j25<br>61-j26<br>60-j27    |      | $\Omega$ $\Omega$ $\Omega$ |

| Read sensitivity for power matching (complex-conjugate matching) in passive mode                                                               | P <sub>WU_PAS</sub>  | Passive mode $f_A=868MHz$ $f_A=915MHz$                                                                                    |      | -9<br>-8                      |      | dBm<br>dBm                 |

| Read sensitivity for power matching (complex-conjugate matching) in battery-assisted mode                                                      | P <sub>WU_BAT</sub>  | Battery-assisted<br>mode;<br>$1.2 < V_{BAT} < 2.0V$<br>$T = 25^{\circ}C$<br>$f_A = 868MHz$<br>$f_A = 915MHz$              |      | -27<br>-27                    |      | dBm<br>dBm                 |

| Battery-low voltage                                                                                                                            | $V_{BAT\_LOW}$       |                                                                                                                           | 1.15 | 1.2                           | 1.25 | V<br><b>T</b> able         |

Table 4

#### **Timing Characteristics**

| Tilling Glaracteristics         |                   |                        |      |      |      |        |

|---------------------------------|-------------------|------------------------|------|------|------|--------|

| Parameters                      | Symbol            | Conditions             | Min. | Тур. | Max. | Unit   |

| Erase / write endurance         | T <sub>CYC</sub>  |                        | 10k  |      |      | Cycles |

| Retention                       | T <sub>RET</sub>  | $T_{OP} = 55^{\circ}C$ | 10   |      |      | Years  |

| Write time for 16 bits / 1 word | T <sub>WR</sub>   |                        | 6.1  | 7.2  | 8.3  | ms     |

| RF fade control time            | T <sub>FADE</sub> | Battery-assisted mode  | 40   | 80   | 175  | ms     |

The activation threshold is defined as the RF power level above which the chip starts operating and is equal to or lower than the read sensitivity

# **Functional Description**

**Memory Organization**

| Memory name | Memory<br>bank | 16-bit bank word (decimal) | 16-bit physical word (decimal) | Contents             |

|-------------|----------------|----------------------------|--------------------------------|----------------------|

|             |                | 0                          | 0                              | IZ:II                |

| DE0ED\/ED   |                | 1                          | 1                              | Kill password        |

| RESERVED    | 002            | 2                          | 2                              | _                    |

|             |                | 3                          | 3                              | Access passwor       |

|             |                | 0                          | 4                              |                      |

| TID         | 40             | 1                          | 5                              | TID / I IID          |

| TID         | 102            | 2                          | 6                              | TID / UID            |

|             |                | 3                          | 7                              |                      |

|             |                | 0                          | RAM                            | CRC-16               |

|             |                | 1                          | 8                              | PC                   |

|             |                | 2                          | 9                              |                      |

| EPC         | 04             | 3                          | 10                             |                      |

| EPC         | 012            | 4                          | 11                             | EPC                  |

|             |                | 5                          | 12                             | EPC                  |

|             |                | 6                          | 13                             |                      |

|             |                | 7                          | 14                             |                      |

| USER        | 112            | 0-44                       | 15-59                          | User data            |

|             |                | 45                         | 60                             | System configuration |

| )           |                |                            |                                | 3                    |

| SYSTEM      |                | 46                         | 61                             | N/A                  |

| SYSTEM      |                | 46<br>47                   | 61<br>62                       |                      |

Table 6: Memory map

The 64-bit TID / UID is programmed and perma-write-locked during manufacturing and before customer delivery. This guarantees the uniqueness of each device on the market. The custom command GetUID allows fast access of the UID and provides more confidence in the uniqueness.

| Memory name<br>bank |   |   |   |   |   |   |     | SYS | STEM              | / 112 |   |   |   |                  |                |     |

|---------------------|---|---|---|---|---|---|-----|-----|-------------------|-------|---|---|---|------------------|----------------|-----|

| 16-bit bank<br>word |   |   |   |   |   |   |     | 45  | <sub>10</sub> (2D | 16)   |   |   |   |                  |                |     |

| Bits (MSB first)    | 0 | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8                 | 9     | Α | В | С | D                | Е              | F   |

| Content             |   |   |   |   |   |   | N/A |     |                   |       |   |   |   | Tamper<br>Status | Battery<br>Low | N/A |

Table 7

| Content       | Description                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------|

| Tamper Status | Volatile bit set to 1 when tamper condition is present                                          |

| Battery Low   | Volatile bit set to 1 when the battery is low i.e. when V <sub>BAT</sub> < V <sub>BAT</sub> LOW |

Table 8

# **EEPROM Delivery state**

The default configuration is as follows:

- □ Unique Identification number (UID / TID)

- □ Version without tamper detection has value E200'B001'XXXX'XXXXh where XXXX'XXXXh is a 32-bit serial number

- □ Version with tamper detection has value E200'B002'XXXX'XXXXh where XXXX'XXXXh is a 32-bit serial number

- □ EPC at value 0000'0000'0000'0000'0000'0000h

- ☐ User data words 0-43 are set to 0000h, User data word 44 is set to an arbitrary value

## **Commands**

## **Command types**

Three sets of commands are defined:

- Mandatory

- Optional

- □ Custom

## **Command codes**

The table below shows all implemented commands in EM4324. For the description of all mandatory and optional commands, please refer to the EPCglobal Class-1 Gen-2 standard. More detailed information on the GetUID custom command is given further below.

| Command code        | Туре      | Function    |  |  |  |

|---------------------|-----------|-------------|--|--|--|

| '00'                | Mandatory | QueryRep    |  |  |  |

| '01'                | Mandatory | ACK         |  |  |  |

| '1000'              | Mandatory | Query       |  |  |  |

| '1001'              | Mandatory | QueryAdjust |  |  |  |

| '1010'              | Mandatory | Select      |  |  |  |

| '11000000'          | Mandatory | NAK         |  |  |  |

| '11000001'          | Mandatory | Req_RN      |  |  |  |

| '11000010'          | Mandatory | Read        |  |  |  |

| '11000011'          | Mandatory | Write       |  |  |  |

| '11000100'          | Mandatory | Kill        |  |  |  |

| '11000101'          | Mandatory | Lock        |  |  |  |

| '11000110'          | Optional  | Access      |  |  |  |

| '11100000 00000000' | Custom    | GetUID      |  |  |  |

#### **GetUID** custom command

|             | Command code      | RN                   |

|-------------|-------------------|----------------------|

| # of bits   | 16                | 16                   |

| Description | 11100000 00000000 | Prior RN16 or handle |

Table 10

The custom command GetUID is implemented as in **Table 10**. It allows an interrogator to read the tag's 64-bit TID / UID with a single command.

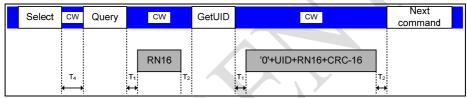

A tag in Reply, Acknowledged, Open or Secured state backscatters {'0', TID / UID, RN16, CRC-16} upon a GetUID command with a valid RN16 or handle (see **Table 11**). The state transition and link timing is the same as for the Ack command. The tag reply is analogous to the tag reply upon a Read command. A link timing example is shown in Fig. 3.

|             | Header | UID       | RN                          | CRC-16               |

|-------------|--------|-----------|-----------------------------|----------------------|

| # of bits   | 1      | 64        | 16                          | 16                   |

| Description | 0      | TID / UID | RN16 (prior RN16 or handle) | CRC-16('0'+TID+RN16) |

Table 11

Fig. 3

#### **Battery assistance**

The pad VBAT allows supplying the chip with an external battery. In case the battery is flat or not present, the chip is supplied by the RF signal on pad A (passive mode). The chip is in Sleep mode in case the RF signal on pad A is below the sensitivity level and behaves like a passive chip below wake-up i.e. it does not reply to any command. The wake-up from Sleep mode corresponds to a power-up of a passive EPC chip and is triggered by the presence of an RF field above the sensitivity level. The chip implements an RF fade control mechanism to overcome momentary nulls that may occur in the RF field. This allows for more reliable sustained communications when operating at very long ranges. The RF fade control time is the time duration that starts when the RF signal on pad A drops below the sensitivity level and ends when the chip declares a loss of the RF field and transition to Sleep mode.

## Near-field mode / parallel resonance matching

By using an inductive coil between the pad A and VSS, it is possible to magnetically couple the chip to an interrogator as used in HF / LF RFID applications. The magnetic / near-field coupling is used to overcome some limitations of electromagnetic / far-field scattering. It is e.g. possible to establish a link through water and other materials that greatly reflect the electromagnetic field but not the magnetic field.

To facilitate the near-field mode an on-chip AC coupling capacitor is implemented so that the coil between the pad A and VSS can be used without the need for an external AC coupling capacitor.

#### **Tamper Detection**

Tamper detection is an optional feature. It is included for all packaged devices and is optional for wafers depending upon the version ordered. The pads/pins TIN and TOUT may be connected via a simple continuity loop, with heat sensitive fuse wire, with sensors having both high and low impedance states, or with external devices controlling an electronic switch such as a MOSFET. The connectivity between TIN and TOUT is checked when the device detects an RF field and enters the Ready state to start communications with a reader. If low impedance is detected, then the *Tamper status* bit is set, otherwise it is cleared. A reader may then read User Memory word 45<sub>10</sub> (2D<sub>16</sub>) to determine if a tamper condition exists.

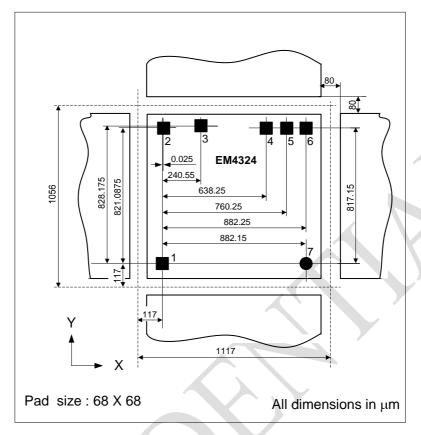

# Chip floor plan

Fig. 4

# **Pad description**

| Pad | Name              | Description             |  |  |

|-----|-------------------|-------------------------|--|--|

| 1   | VSS               | Antenna and battery-    |  |  |

| 2   | VBAT 2)           | Battery+                |  |  |

| 3   | TST <sup>2)</sup> | N/A - Test purpose only |  |  |

| 4   | TST2 3)           | N/A - Test purpose only |  |  |

| 5   | TIN 3)            | Tamper input            |  |  |

| 6   | TOUT 3)           | Tamper output           |  |  |

| 7   | Α                 | Antenna+                |  |  |

Table 12

Note 2: The pads VBAT and TST can be shorted together to ease inlay assembly

Note 3: The pads TST2, TIN and TOUT can be shorted together to ease inlay assembly (not so for tamper detection versions)

# Package information:

EM4324 is available in TSSOP-8 package. More details on package dimensions, pin-out and ordering information are below.

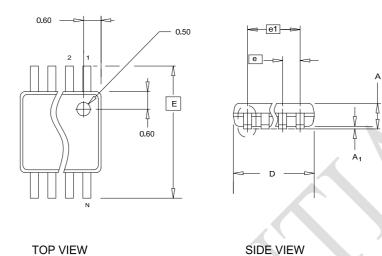

# Package dimensions

| s      |            |          |      |        |  |

|--------|------------|----------|------|--------|--|

| Y      | COMMON     |          |      |        |  |

| M<br>B | DIMENSIONS |          |      |        |  |

| O<br>L | MIN.       | NOM.     | MAX. | T<br>E |  |

| Α      |            |          | 1.10 |        |  |

| A 1    | 0.05       | 0.10     | 0.15 |        |  |

| D      |            | 3.00 BSC |      |        |  |

| E      | 4.90 BSC   |          |      |        |  |

| е      | 0.65 BSC   |          |      |        |  |

| e1     | 1.95 BSC   |          |      |        |  |

| N      |            | 8        |      |        |  |

Note 4: BSC - Basic spacing between centers

# **TSSOP-8 Pin description**

| Pin | Name | Description          |

|-----|------|----------------------|

| 1   | Α    | Antenna+             |

| 2   | NC   | NC                   |

| 3   | TOUT | Tamper output        |

| 4   | TIN  | Tamper input         |

| 5   | TST2 | N/A                  |

| 6   | TST  | N/A                  |

| 7   | VBAT | Battery+             |

| 8   | VSS  | Antenna and battery- |

Table 13

Fig. 5

# **Package Ordering Information**

| Part Number   | Tamper Detection | Package | Delivery Form |  |

|---------------|------------------|---------|---------------|--|

| EM4324V2TP8B+ | Yes              | TSSOP-8 | Tape          |  |

## **Ordering Information**

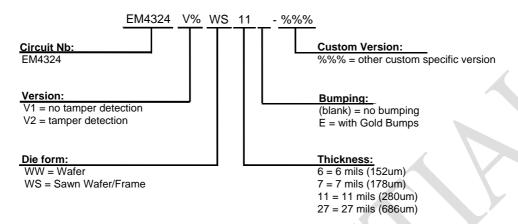

The following charts show the general offering. For detailed Part Number to order, please see the table "Standard Versions" below.

#### Die form

Fig. 6

#### Remarks:

- ☐ For ordering, please, use table of "Standard Version" table below.

- ☐ For specifications of Delivery Form, including gold bumps, tape and bulk, as well as possible other delivery form or packages, please, contact EM Microelectronic-Marin S.A.

#### **Standard Versions & Samples:**

For samples, please, order exclusively:

The versions below are considered standards and should be readily available. For other versions or other delivery form, please contact EM Microelectronic-Marin S.A.

| Part Number     | Tamper Detection | Package/Die Form                              | Delivery Form       |

|-----------------|------------------|-----------------------------------------------|---------------------|

| EM4324V1WS7E    | No               | Sawn wafer / bumped die – thickness of 7 mils | Wafer sawn on frame |

| EM4324V2WS7E    | Yes              | Sawn wafer / bumped die – thickness of 7 mils | Wafer sawn on frame |

| EM4324VXYYY-%%% |                  | Custom                                        | Custom              |

Table 15

## **Product Support**

Check our web site under Products/RF Identification section. Questions can be sent to info@emmicroelectronic.com.

EM Microelectronic-Marin SA (EM) makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in EM's General Terms of Sale located on the Company's web site. EM assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of EM are granted in connection with the sale of EM products, expressly or by implications. EM's products are not authorized for use as components in life support devices or systems.